Shell Developer Guide for Open FPGA Stack: Intel® FPGA SmartNIC N6000-PL / Intel® FPGA SmartNIC N6001-PL PCIe Attach¶

Last updated: December 10, 2024

1. Introduction¶

1.1. About This Document¶

This document serves as a guide for OFS Agilex PCIe Attach developers targeting the Intel® FPGA SmartNIC N6000-PL and Intel® FPGA SmartNIC N6001-PL. The following topics are covered in this guide:

- Compiling the OFS Agilex PCIe Attach FIM design

- Simulating the OFS Agilex PCIe Attach design

- Customizing the OFS Agilex PCIe Attach FIM design

- Configuring the FPGA with an OFS Agilex PCIe Attach FIM design

The FIM Development Walkthroughs Table lists all of the walkthroughs provided in this guide. These walkthroughs provide step-by-step instructions for performing different FIM Development tasks.

Table: FIM Development Walkthroughs

1.1.1 Knowledge Pre-Requisites¶

It is recommended that you have the following knowledge and skills before using this developer guide.

- Basic understanding of OFS and the difference between OFS designs. Refer to the OFS Welcome Page.

- Review the release notes for the Agilex® 7 PCIe Attach Reference Shells, with careful consideration of the Known Issues.

- Review of Getting Started Guide: OFS for Agilex® 7 PCIe Attach FPGAs (Intel® FPGA SmartNIC N6001-PL/N6000-PL).

- FPGA compilation flows using Quartus® Prime Pro Edition Software.

- Static Timing closure, including familiarity with the Timing Analyzer tool in Quartus® Prime Pro Edition Software, applying timing constraints, Synopsys* Design Constraints (.sdc) language and Tcl scripting, and design methods to close on timing critical paths.

- RTL (System Verilog) and coding practices to create synthesized logic.

- RTL simulation tools.

- Quartus® Prime Pro Edition Software Signal Tap Logic Analyzer tool software.

1.2. FIM Development Theory¶

This section will help you understand how the OFS Agilex PCIe Attach FIM can be developed to fit your design goals.

The Default FIM Features section provides general information about the default features of the OFS Agilex PCIe Attach FIM so you can become familiar with the default design. For more detailed information about the FIM architecture, refer to the Shell Technical Reference Manual: OFS for Agilex® 7 PCIe Attach FPGAs.

The Customization Options section then gives suggestions of how this default design can be customized. Step-by-step walkthroughs for many of the suggested customizations are later described in the FIM Customization section.

FIM development for a new acceleration card generally consists of the following steps:

- Install OFS and familiarize yourself with provided scripts and source code

- Develop high level design with your specific functionality

- Determine requirements and key performance metrics

- Select IP cores

- Select FPGA device

- Develop software memory map

- Select and implement FIM Physical interfaces including:

- External clock sources and creation of internal PLL clocks

- General I/O

- Ethernet modules

- External memories

- FPGA programming methodology

- Develop device physical implementation

- FPGA device pin assignment

- Create logic lock regions

- Create of timing constraints

- Create Quartus Prime Pro FIM test project and validate:

- Placement

- Timing constraints

- Build script process

- Review test FIM FPGA resource usage

- Select FIM to AFU interfaces and development of PIM

- Implement FIM design

- Develop RTL

- Instantiate IPs

- Develop test AFU to validate FIM

- Develop unit and device level simulation

- Develop timing constraints and build scripts

- Perform timing closure and build validation

- Create FIM documentation to support AFU development and synthesis

- Software Device Feature discovery

- Integrate, validate, and debug hardware/software

- Prepare for high volume production

1.2.1 Default FIM Features¶

1.2.1.1 Top Level¶

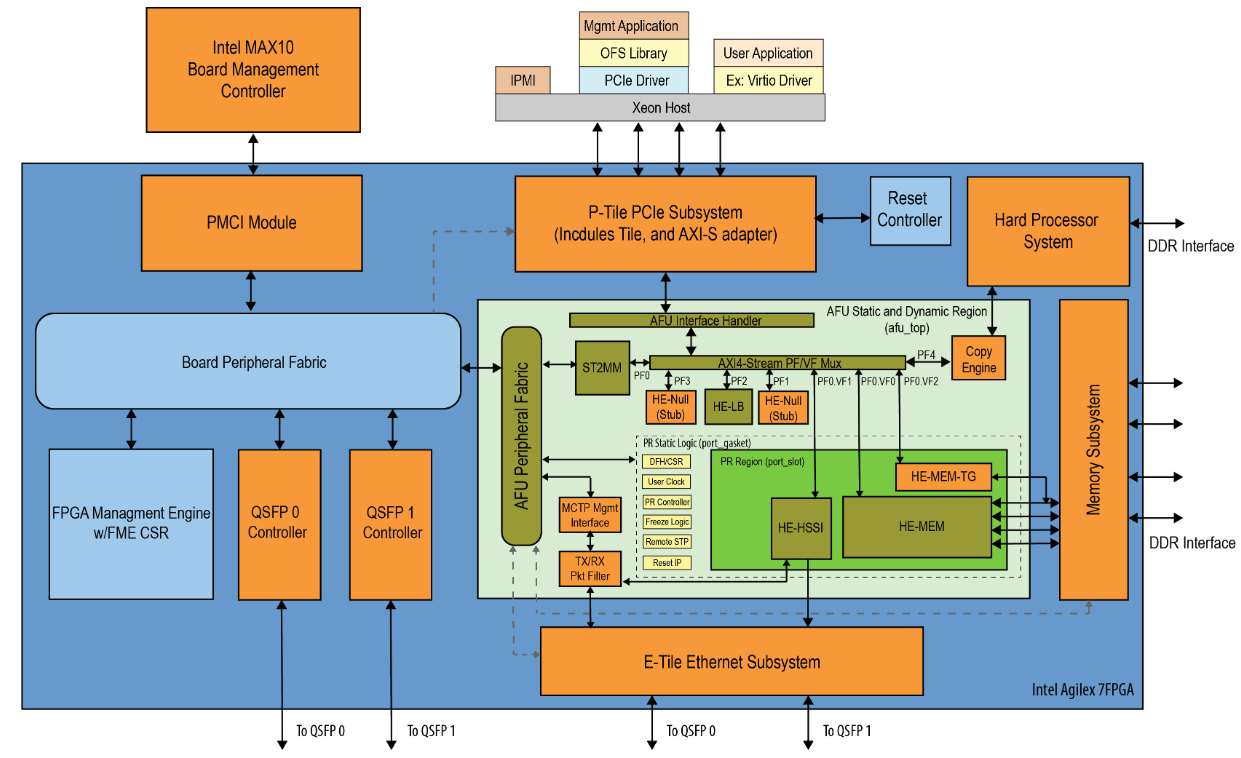

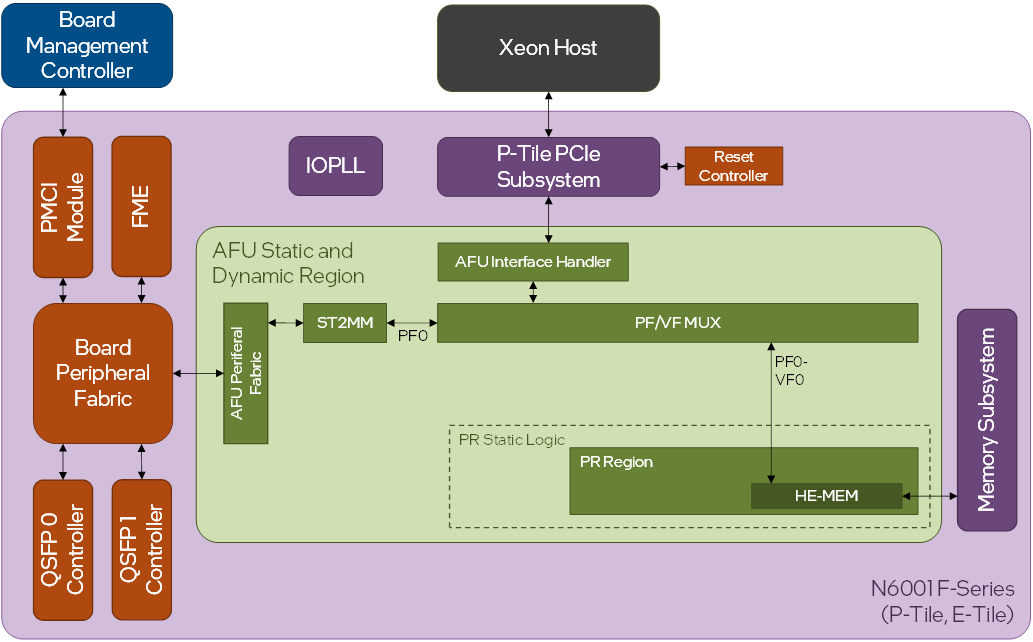

The top level block diagram for the OFS Agilex PCIe Attach reference design is shown below.

Figure: OFS Agilex PCIe Attach FIM Top-Level Diagram

1.2.1.2 Interfaces¶

The key interfaces in the OFS Agilex PCIe Attach design are listed in the Release Capabilities tables below. They describe the capabilities of the n6001 and n6000 hardware as well as the capabilities of the default OFS Agilex PCIe Attach reference designs targeting the n6001 and the n6000.

Table: Intel® FPGA SmartNIC N6001-PL OFS Release Capabilities

| Interface | Intel® FPGA SmartNIC N6001-PL Hardware Capabilities | n6001 OFS Agilex PCIe Attach Reference Design Implementation |

|---|---|---|

| Host Interface | PCIe Gen4x16 | PCIe Gen4x16 |

| Network Interface | 2 x QSFP-28/56 cages | 2x4x25GbE | 2x1x100GbE | 2x4x10GbE |

| External Memory | 5xDDR4 DIMMs sockets - 40-bits (1 available for HPS) | 4xDDR4 - 2400MHz - 4GB (1Gb x 32) - 32-bits - No ECC1xDDR4 - 2400MHz - 1GB (256Mb x 32 with 256 Mb x8 ECC) - 40-bits - With ECC - For HPS |

Table: Intel® FPGA SmartNIC N6000-PL OFS Release Capabilities

| Interface | Intel® FPGA SmartNIC N6000-PL Hardware Capabilities | n6000 OFS Agilex PCIe Attach Reference Design Implementation |

|---|---|---|

| Host Interface | To Agilex 7: PCIe Gen4x8 To E810: PCIe Gen4x8 | To Agilex 7: PCIe Gen4x8 To E810: PCIe Gen4x8 |

| Network Interface | 2 x QSFP-28/56 cages | 2x2x100GbE |

| External Memory | 5xDDR4 DIMMs sockets - 40-bits (1 available for HPS) | Not enabled by default, but can support: 4xDDR4 - 2400MHz - 4GB (1Gb x 32) - 32-bits - No ECC1xDDR4 - 2400MHz - 1GB (256Mb x 32 with 256 Mb x8 ECC) - 40-bits - With ECC - For HPS |

1.2.1.3 Subsystems¶

The FIM Subsystems Table describes the Platform Designer IP subsystems used in the OFS Agilex PCIe Attach n6001 FIM.

Table: FIM Subsystems

| Subsystem | User Guide | Document ID |

|---|---|---|

| PCIe Subsystem | PCIe Subsystem Intel FPGA IP User Guide for Intel Agilex OFS | N/A |

| Memory Subsystem | Memory Subsystem Intel FPGA IP User Guide for Intel Agilex OFS | 686148[1] |

| Ethernet Subsystem | Ethernet Subsystem Intel FPGA IP User Guide | 773413[1] |

[1] You must request entitled access to these documents.

1.2.1.4 Host Exercisers¶

The default AFU workload in the OFS Agilex PCIe Attach n6001/n6000 FIM contains several modules called Host Exercisers which are used to exercise the interfaces on the board. The Host Exerciser Descriptions Table describes these modules.

Table: Host Exerciser Descriptions

| Name | Acronym | Description | OPAE Command |

|---|---|---|---|

| Host Exerciser Loopback | HE-LB | Used to exercise and characterize host to FPGA data transfer. | host_exerciser |

| Host Exerciser Memory | HE_MEM | Used to exercise and characterize host to Memory data transfer. | host_exerciser |

| Host Exerciser Memory Traffic Generator | HE_MEM_TG | Used to exercise and test available memory channels with a configurable traffic pattern. | mem_tg |

| Host Exerciser High Speed Serial Interface | HE-HSSI | n6001: Used to exercise and characterize HSSI interfaces. n6000: Used to pass through data between the E810 to the QSFPs. | hssi |

The host exercisers can be removed from the design at compile-time using command line arguments for the build script.

1.2.1.5 Module Access via APF/BPF¶

The OFS Agilex PCIe Attach n6001 FIM uses AXI4-Lite interconnect logic named the AFU Peripheral Fabric (APF) and Board Peripheral Fabric (BPF) to access the registers of the various modules in the design. The APF/BPF modules define master/slave interactions, namely between the host software and AFU and board peripherals. The APF Address Map Table describes the address mapping of the APF, followed by the BPF Address Map Table which describes the address mapping of the BPF.

Table: APF Address Map

| Address | Size (Bytes) | Feature |

|---|---|---|

| 0x00000–0x3FFFF | 256K | Board Peripherals (See BPF Address Map table) |

| 0x40000 – 0x4FFFF | 64K | ST2MM |

| 0x50000 – 0x5FFFF | 64K | Reserved |

| 0x60000 – 0x60FFF | 4K | UART |

| 0x61000 – 0x6FFFF | 4K | Reserved |

| 0x70000 – 0x7FFFF | 56K | PR Gasket:4K= PR Gasket DFH, control and status4K= Port DFH4K=User Clock52K=Remote STP |

| 0x80000 – 0x80FFF | 4K | AFU Error Reporting |

Table: BPF Address Map

| Address | Size (Bytes) | Feature |

|---|---|---|

| 0x00000 - 0x0FFFF | 64K | FME |

| 0x10000 - 0x10FFF | 4K | PCIe |

| 0x11000 - 0x11FFF | 4K | Reserved |

| 0x12000 - 0x12FFF | 4K | QSFP0 |

| 0x13000 - 0x13FFF | 4K | QSFP1 |

| 0x14000 - 0x14FFF | 4K | HSSI |

| 0x15000 - 0x15FFF | 4K | EMIF |

| 0x20000 - 0x3FFFF | 128K | PMCI Controller |

1.2.2 Customization Options¶

OFS is designed to be easily customizable to meet your design needs. The OFS FIM Customization Examples Table lists the general user flows for OFS Agilex PCIe Attach n6001/n6000 FIM development, along with example customizations for each user flow, plus links to step-by-step walkthroughs where available.

Table: OFS FIM Customization Examples

1.3 Development Environment¶

This section describes the components required for OFS FIM development, and provides a walkthrough for setting up the environment on your development machine.

Note that your development machine may be different than your deployment machine where the FPGA acceleration card is installed. FPGA development work and deployment work can be performed either on the same machine, or on different machines as desired. Please see the Getting Started Guide: OFS for Agilex® 7 PCIe Attach FPGAs (Intel® FPGA SmartNIC N6001-PL/N6000-PL) for instructions on setting up the environment for deployment machines.

1.3.1 Development Tools¶

The Development Environment Table describes the Best Known Configuration (BKC) for the tools that are required for OFS FIM development.

Table: Development Environment BKC

| Component | Version | Installation Walkthrough |

|---|---|---|

| Operating System | RedHat® Enterprise Linux® (RHEL) 8.6 | N/A |

| Quartus® Prime Pro Edition Software | Quartus Prime Pro Version 23.4 for Linux + Patches 0.17 patch (PCIe) | Section 1.3.1.1 |

| Python | 3.6.8 or later | N/A |

| GCC | 8.5.0 or later | N/A |

| cmake | 3.15 or later | N/A |

| FIM Source Files | ofs-2024.1-1 | Section 1.3.2.1 |

1.3.1.1 Walkthrough: Install Quartus Prime Pro Software¶

Intel Quartus Prime Pro Version 23.4 is verified to work with the latest OFS release ofs-2024.1-1. However, you have the option to port and verify the release on newer versions of Intel Quartus Prime Pro software.

Use RedHat® Enterprise Linux® (RHEL) 8.6 for compatibility with your development flow and also testing your FIM design in your platform.

Prior to installing Quartus:

-

Ensure you have at least 64 GB of free space for Quartus Prime Pro installation and your development work.

- Intel® recommends that your system be configured to provide virtual memory equal in size or larger than the recommended physical RAM size that is required to process your design.

- The disk space may be significantly more based on the device families included in the install. Prior to installation, the disk space should be enough to hold both zipped tar files and uncompressed installation files. After successful installation, delete the downloaded zipped files and uncompressed zip files to release the disk space.

-

Perform the following steps to satisfy the required dependencies.

$ sudo dnf install -y gcc gcc-c++ make cmake libuuid-devel rpm-build autoconf automake bison boost boost-devel libxml2 libxml2-devel make ncurses grub2 bc csh flex glibc-locale-source libnsl ncurses-compat-libsApply the following configurations.

-

Create the default installation path:

/intelFPGA_pro/ , where is the default path of the Linux workstation, or as set by the system administrator and is your Quartus version number. The installation path must satisfy the following requirements:

- Contain only alphanumeric characters

- No special characters or symbols, such as !$%@^&*<>,

- Only English characters

- No spaces

-

Download your required Quartus Prime Pro Linux version here.

-

Install required Quartus patches. The Quartus patch

.runfiles can be found in the Assets tab on the OFS Release GitHub page. The patches for this release are 0.17 patch (PCIe). -

After running the Quartus Prime Pro installer, set the PATH environment variable to make utilities

quartus,jtagconfig, andquartus_pgmdiscoverable. Edit your bashrc file~/.bashrcto add the following line:export PATH=<Quartus install directory>/quartus/bin:$PATH export PATH=<Quartus install directory>/qsys/bin:$PATHFor example, if the Quartus install directory is /home/intelFPGA_pro/23.4 then the new line is:

-

Verify, Quartus is discoverable by opening a new shell:

1.3.2 FIM Source Files¶

The source files for the OFS Agilex PCIe Attach FIM are provided in the following repository: https://github.com/OFS/ofs-agx7-pcie-attach/releases/tag/ofs-2024.1-1.

Some essential directories in the repository are described as follows:

ofs-agx7-pcie-attach

| syn // Contains files related to synthesis

| | board // Contains synthesis files for several cards, including the n6001 and n6000

| | | n6001 // Contains synthesis files for n6001 and n6000

| | | | setup // Contains setup files, including pin constraints and location constraints

| | | | syn_top // Contains Quartus project files

| verification // Contains files for UVM testing

| ipss // Contains files for IP Sub-Systems

| | qsfp // Contains source files for QSFP Sub-System

| | hssi // Contains source files for HSSI Sub-System

| | pmci // Contains source files for PMCI Sub-System (not used in F-Tile FIM)

| | pcie // Contains source files for PCIe Sub-System

| | mem // Contains source files for Memory Sub-System

| sim // Contains simulation files

| | unit_test // Contains files for all unit tests

| | | scripts // Contains script to run regression unit tests

| license // Contains Quartus patch

| ofs-common // Contains files which are common across OFS platforms

| | verification // Contains common UVM files

| | scripts // Contains common scripts

| | | common

| | | | syn // Contains common scripts for synthesis, including build script

| | | | sim // Contains common scripts for simulation

| | tools // Contains common tools files

| | | mk_csr_module // Contains common files for CSR modules

| | | fabric_generation // Contains common files for APF/BPF fabric generation

| | | ofss_config // Contains common files for OFSS configuration tool

| | | | ip_params // Contains default IP parameters for certain Sub-Systems when using OFSS

| | src // Contains common source files, including host exercisers

| tools //

| | ofss_config // Contains top level OFSS files for each pre-made board configuration

| | | hssi // Contains OFSS files for Ethernet-SS configuraiton

| | | memory // Contains OFSS files for Memory-SS configuration

| | | pcie // Contains OFSS files for PCIe-SS configuration

| | | iopll // Contains OFSS files for IOPLL configuration

| src // Contains source files for Agilex PCIe Attach FIM

| | pd_qsys // Contains source files related to APF/BPF fabric

| | includes // Contains source file header files

| | top // Contains top-level source files, including design top module

| | afu_top // Contains top-level source files for AFU

1.3.2.1 Walkthrough: Clone FIM Repository¶

Perform the following steps to clone the OFS Agilex® 7 PCIe Attach FIM Repository:

-

Create a new directory to use as a clean starting point to store the retrieved files.

-

Clone GitHub repository using the HTTPS git method

-

Check out the correct tag of the repository

-

Ensure that

ofs-commonhas been cloned as wellExample output:

1.3.3 Environment Variables¶

The OFS FIM compilation and simulation scripts require certain environment variables be set prior to execution.

1.3.3.1 Walkthrough: Set Development Environment Variables¶

Perform the following steps to set the required environment variables. These environment variables must be set prior to simulation or compilation tasks so it is recommended that you create a script to set these variables.

-

Navigate to the top level directory of the cloned OFS FIM repository.

-

Set project variables

-

Set variables based on your development environment

# Set proxies if required for your server export http_proxy=<YOUR_HTTP_PROXY> export https_proxy=<YOUR_HTTPS_PROXY> export ftp_proxy=<YOUR_FTP_PROXY> export socks_proxy=<YOUR_SOCKS_PROXY> export no_proxy=<YOUR_NO_PROXY> # Set Quartus license path export LM_LICENSE_FILE=<YOUR_LM_LICENSE_FILE> # Set Synopsys License path (if using Synopsys for simulation) export DW_LICENSE_FILE=<YOUR_DW_LICENSE_FILE> export SNPSLMD_LICENSE_FILE=<YOUR_SNPSLMD_LICENSE_FILE> # Set Quartus Installation Directory - e.g. $QUARTUS_ROOTDIR/bin contains Quartus executables export QUARTUS_ROOTDIR=<YOUR_QUARTUS_INSTALLATION_DIRECTORY> # Set the Tools Directory - e.g. $TOOLS_LOCATION contains the 'synopsys' directory if you are using Synopsys. Refer to the $VCS_HOME variable for an example. export TOOLS_LOCATION=<YOUR_TOOLS_LOCATION> -

Set generic environment variables

# Set Work directory export WORKDIR=$OFS_ROOTDIR # Set Quartus Tools variables export QUARTUS_HOME=$QUARTUS_ROOTDIR export QUARTUS_INSTALL_DIR=$QUARTUS_ROOTDIR export QUARTUS_ROOTDIR_OVERRIDE=$QUARTUS_ROOTDIR export QUARTUS_VER_AC=$QUARTUS_ROOTDIR export IP_ROOTDIR=$QUARTUS_ROOTDIR/../ip export IMPORT_IP_ROOTDIR=$IP_ROOTDIR export QSYS_ROOTDIR=$QUARTUS_ROOTDIR/../qsys/bin # Set Verification Tools variables (if running simulations) export DESIGNWARE_HOME=$TOOLS_LOCATION/synopsys/vip_common/vip_Q-2020.03A export UVM_HOME=$TOOLS_LOCATION/synopsys/vcsmx/S-2021.09-SP1/linux64/rhel/etc/uvm export VCS_HOME=$TOOLS_LOCATION/synopsys/vcsmx/S-2021.09-SP1/linux64/rhel export MTI_HOME=$QUARTUS_ROOTDIR/../questa_fse export VERDIR=$OFS_ROOTDIR/verification export VIPDIR=$VERDIR # Set OPAE variables export OPAE_SDK_REPO_BRANCH=release/2.12.0 # Set PATH to include compilation and simulation tools export PATH=$QUARTUS_HOME/bin:$QUARTUS_HOME/../qsys/bin:$QUARTUS_HOME/sopc_builder/bin/:$IOFS_BUILD_ROOT/opae-sdk/install-opae-sdk/bin:$MTI_HOME/linux_x86_64/:$MTI_HOME/bin/:$DESIGNWARE_HOME/bin:$VCS_HOME/bin:$PATH

1.3.4 Walkthrough: Set Up Development Environment¶

This walkthrough guides you through the process of setting up your development environment in preparation for FIM development. This flow only needs to be done once on your development machine.

-

Ensure that Quartus Prime Pro Version 23.4 for Linux with Agilex® 7 FPGA device support is installed on your development machine. Refer to the Install Quartus Prime Pro Software section for step-by-step installation instructions.

- Verify version number

Example Output:

- Verify version number

-

Ensure that all support tools are installed on your development machine, and that they meet the version requirements.

-

Python 3.6.8 or later

-

Verify version number

Example Output:

-

-

GCC 8.5.0 or later

-

Verify version number

Example output:

-

-

cmake 3.15 or later

-

Verify version number

Example output:

-

-

-

Clone the ofs-agx7-pcie-attach repository. Refer to the Clone FIM Repository section for step-by-step instructions.

-

Install UART IP license patch

.02.-

Navigate to the

licensedirectory -

Install Patch 0.02

-

-

Install Quartus Patches 0.17 patch (PCIe). All required patches are provided in the Assets of the OFS FIM Release: https://github.com/OFS/ofs-agx7-pcie-attach/releases/tag/ofs-2024.1-1

-

Extract and unzip the

patch-agx7-2024-1.tar.gzfile. -

Run each patch

.runfile. As an example:

-

-

Verify that patches have been installed correctly. They should be listed in the output of the following command.

-

Set required environment variables. Refer to the Set Development Environment Variables section for step-by-step instructions.

This concludes the walkthrough for setting up your development environment. At this point you are ready to begin FIM development.

2. FIM Compilation¶

This section describes the process of compiling OFS FIM designs using the provided build scripts. It contains two main sections:

- Compilation Theory - Describes the theory behind FIM compilation

- Compilation Flows - Describes the process of compiling a FIM

The walkthroughs provided in this section are:

2.1 Compilation Theory¶

This section describes the theory behind FIM compilation.

2.1.1 FIM Build Script¶

The OFS Common Repository contains a script named build_top.sh which is used to build OFS FIM designs and generate output files that can be programmed to the board. After cloning the OFS FIM repository (with the ofs-common repository included), the build script can be found in the following location:

The usage of the build_top.sh script is as follows:

build_top.sh [-k] [-p] [-e] [--stage=<action>] [--ofss=<ip_config>] <build_target>[:<fim_options>] [<work_dir_name>]

| Field | Options | Description | Requirement |

|---|---|---|---|

-k |

None | Keep. Preserves and rebuilds within an existing work tree instead of overwriting it. | Optional |

-p |

None | When set, and if the FIM supports partial reconfiguration, a PR template tree is generated at the end of the FIM build. The PR template tree is located in the top of the work directory but is relocatable and uses only relative paths. See $OFS_ROOTDIR/syn/common/scripts generate_pr_release.sh for details. | Optional |

-e |

None | Run only Quartus analysis and elaboration. It completes the setup stage, passes -end synthesis to the Quartus compilation flow and exits without running the finish stage. |

Optional |

--stage |

all | setup | compile | finish |

Controls which portion of the OFS build is run. - all: Run all build stages (default) - setup: Initialize a project in the work directory - compile: Run the Quartus compilation flow on a project that was already initialized with setup - finish: Complete OFS post-compilation tasks, such as generating flash images and, if -p is set, generating a release. |

Optional |

--ofss |

<ip_config> |

Used to modify IP, such as the PCIe SS, using .ofss configuration files. This parameter is consumed during the setup stage and IP is updated only inside the work tree. More than one .ofss file may be passed to the --ofss switch by concatenating them separated by commas. For example: --ofss config_a.ofss,config_b.ofss. |

Optional |

<build_target> |

n6000 | n6001 | fseries-dk | iseries-dk |

Specifies which board is being targeted. | Required |

<fim_options> |

flat | null_he_lb | null_he_hssi | null_he_mem | null_he_mem_tg | no_hssi |

Used to change how the FIM is built. • flat - Compiles a flat design (no PR assignments). This is useful for bringing up the design on a new board without dealing with PR complexity. • null_he_lb - Replaces the Host Exerciser Loopback (HE_LBK) with he_null. • null_he_hssi - Replaces the Host Exerciser HSSI (HE_HSSI) with he_null. • null_he_mem - Replaces the Host Exerciser Memory (HE_MEM) with he_null. • null_he_mem_tg - Replaces the Host Exerciser Memory Traffic Generator with he_null. • no_hssi - Removes the HSSI-SS from the FIM. More than one FIM option may be passed included in the <fim_options> list by concatenating them separated by commas. For example: <build_target>:flat,null_he_lb,null_he_hssi |

Optional |

<work_dir_name> |

String | Specifies the name of the work directory in which the FIM will be built. If not specified, the default target is $OFS_ROOTDIR/work |

Optional |

Refer to Compile OFS FIM which provides step-by-step instructions for running the build_top.sh script with some of the different available options.

2.1.1.1 Build Work Directory¶

The build script copies source files from the existing cloned repository into the specified work directory, which are then used for compilation. As such, any changes made in the base source files will be included in all subsequent builds, unless the -k option is used, in which case an existing work directories files are used as-is. Likewise, any changes made in a work directory is only applied to that work directory, and will not be updated in the base repository by default. When using OFSS files to modify the design, the build script will create a work directory and make the modifications in the work directory.

2.1.1.2 Null Host Exercisers¶

An HE_NULL FIM refers to a design with one, some, or all of the Host Exercisers replaced by he_null blocks. The he_null is a minimal block with CSRs that responds to PCIe MMIO requests in order to keep PCIe alive. You may use any of the build flows (flat, in-tree, out-of-tree) with the HE_NULL compile options. The HE_NULL compile options are as follows:

null_he_lb- Replaces the Host Exerciser Loopback (HE_LBK) withhe_nullnull_he_hssi- Replaces the Host Exerciser HSSI (HE_HSSI) withhe_nullnull_he_mem- Replaces the Host Exerciser Memory (HE_MEM) withhe_nullnull_he_mem_tg- Replaces the Host Exerciser Memory Traffic Generator withhe_null

The Compile OFS FIM section gives step-by-step instructions for this flow.

2.1.2 OFSS File Usage¶

The OFS FIM build script can use OFSS files to easily customize design IP prior to compilation using preset configurations. The OFSS files specify certain parameters for different IPs. Using OFSS is provided as a convenience feature for building FIMs. The Provided OFSS Files table below describes the pre-made OFSS files for the n6001 that can be found in the $OFS_ROOTDIR/tools/ofss_config directory. Only the OFSS files listed in this table are compatible with the n6001 In order to compile an n6001 FIM, you must supply OFSS files corresponding to each IP that is present in your design.

Table: Provided OFSS Files

| OFSS File Name | Location | Type | Description | Supported Board |

|---|---|---|---|---|

n6001.ofss |

$OFS_ROOTDIR/tools/ofss_config |

Top | Includes the following OFSS files: • n6001_base.ofss • pcie_host.ofss • iopll.ofss • memory.ofss |

N6001 |

n6001_2pf.ofss |

$OFS_ROOTDIR/tools/ofss_config |

Top | Includes the following OFSS files: • n6001_base.ofss • pcie_2pf.ofss • iopll.ofss • memory.ofss |

N6001 |

n6001_1pf_1vf.ofss |

$OFS_ROOTDIR/tools/ofss_config |

Top | Includes the following OFSS files: • n6001_base.ofss • pcie_1pf_1vf.ofss • iopll.ofss • memory.ofss |

N6001 |

n6000.ofss |

$OFS_ROOTDIR/tools/ofss_config |

Top | Includes the following OFSS files: • n6000_base.ofss • pcie_host_n6000.ofss • iopll_n6000.ofss • hssi_4x100.ofss |

N6000 |

n6001_base.ofss |

$OFS_ROOTDIR/tools/ofss_config |

ofs | Defines certain attributes of the design, including the platform name, device family, fim type, part number, and device ID. | N6001 |

n6000_base.ofss |

$OFS_ROOTDIR/tools/ofss_config |

ofs | Defines certain attributes of the design, including the platform name, device family, fim type, part number, and device ID. | N6000 |

pcie_host.ofss |

$OFS_ROOTDIR/tools/ofss_config/pcie |

pcie | Defines the PCIe Subsystem for the N6001 with the following configuration: • PF0 (3 VFs) • PF1 (0 VFs) • PF2 (0 VFs) • PF3 (0 VFs) • PF4 (0 VFs) | N6001 |

pcie_2pf.ofss |

$OFS_ROOTDIR/tools/ofss_config/pcie |

pcie | Defines the PCIe Subsystem with the following configuration: • PF0 (0 VFs) • PF1 (0 VFs) | N6001 |

pcie_1pf_1vf.ofss |

$OFS_ROOTDIR/tools/ofss_config/pcie |

pcie | Defines the PCIe Subsystem with the following configuration: • PF0 (1 VF) | N6001 |

pcie_host_n6000.ofss |

$OFS_ROOTDIR/tools/ofss_config/pcie |

pcie | Defines the PCIe Subsystem for the N6000 with the following configuration: • PF0 (3 VFs) • PF1 (0 VFs) • PF2 (0 VFs) • PF3 (0 VFs) • PF4 (0 VFs) | N6001 |

iopll.ofss |

$OFS_ROOTDIR/tools/ofss_config/iopll |

iopll | Sets the IOPLL frequency to 470 MHz |

N6001 |

iopll_n6000.ofss |

$OFS_ROOTDIR/tools/ofss_config/iopll |

iopll | Sets the IOPLL frequency to 350 MHz |

N6000 |

memory.ofss |

$OFS_ROOTDIR/tools/ofss_config/memory |

memory | Defines the memory IP preset file to be used during the build as n6001 |

N6001 | N6000 [1] |

hssi_8x25.ofss |

$OFSS_ROOTDIR/tools/ofss_config/hssi |

hssi | Defines the Ethernet-SS IP configuration to be 8x25 GbE | N6001 |

hssi_8x10.ofss |

$OFSS_ROOTDIR/tools/ofss_config/hssi |

hssi | Defines the Ethernet-SS IP configuration to be 8x10 GbE | N6001 |

hssi_2x100.ofss |

$OFSS_ROOTDIR/tools/ofss_config/hssi |

hssi | Defines the Ethernet-SS IP configuration to be 2x100 GbE | N6001 |

hssi_4x100.ofss |

$OFSS_ROOTDIR/tools/ofss_config/hssi |

hssi | Defines the Ethernet-SS IP configuration to be 4x100 GbE | N6000 |

[1] The memory.ofss file can be used for the N6000, however, the default N6000 FIM does not implement the Memory Sub-system. Refer to Section 4.7.2 for step-by-step instructions on how to enable the Memory sub-system

There can typically be three sections contained within an OFSS file.

-

[include]- This section of an OFSS file contains elements separated by a newline, where each element is the path to an OFSS file that is to be included for configuration by the OFSS Configuration Tool. Ensure that any environment variables (e.g.

$OFS_ROOTDIR) is set correctly. The OFSS Config tool uses breadth first search to include all of the specified OFSS files; the ordering of OFSS files does not matter

- This section of an OFSS file contains elements separated by a newline, where each element is the path to an OFSS file that is to be included for configuration by the OFSS Configuration Tool. Ensure that any environment variables (e.g.

-

[ip]- This section of an OFSS file contains a key value pair that allows the OFSS Config tool to determine which IP configuration is being passed in. The currently supported values of IP are

ofs,iopll,pcie,memory, andhssi.

- This section of an OFSS file contains a key value pair that allows the OFSS Config tool to determine which IP configuration is being passed in. The currently supported values of IP are

-

[settings]- This section of an OFSS file contains IP specific settings. Refer to an existing IP OFSS file to see what IP settings are set. For the IP type `ofss``, the settings will be information of the OFS device (platform, family, fim, part #, device_id)

2.1.2.1 Platform OFSS File¶

The <platform>.ofss file (e.g. $OFS_ROOTDIR/tools/ofss_config/n6001.ofss) is the platform level OFSS wrapper file. This is typically the OFSS file that is provided to the build script. It only contains an include section which lists all other OFSS files that are to be used when the <platform>.ofss file is passed to the build script.

The generic structure of a <platform>.ofss file is as follows:

[include]

<PATH_TO_PLATFORM_BASE_OFSS_FILE>

<PATH_TO_PCIE_OFSS_FILE>

<PATH_TO_IOPLL_OFSS_FILE>

<PATH_TO_MEMORY_OFSS_FILE>

<PATH_TO_HSSI_OFSS_FILE>

2.1.2.2 OFS IP OFSS File¶

An OFSS file with IP type ofs (e.g. $OFS_ROOTDIR/tools/ofss_config/n6001_base.ofss) contains board specific information for the target board.

Currently supported configuration options for an OFSS file with IP type ofs are described in the OFS IP OFSS File Options table.

Table: OFS IP OFSS File Options

| Section | Parameter | n6001 Default Value | n6000 Default Value |

|---|---|---|---|

[ip] |

type |

ofs |

ofs |

[settings] |

platform |

n6001 |

n6000 |

family |

agilex |

agilex |

|

fim |

base_x16 |

base_x16 |

|

part |

AGFB014R24A2E2V |

AGFB014R24A2E2V |

|

device_id |

6001 |

6000 |

2.1.2.3 PCIe IP OFSS File¶

An OFSS file with IP type pcie (e.g. $OFS_ROOTDIR/tools/ofss_config/pcie/pcie_host.ofss) is used to configure the PCIe-SS in the FIM.

The PCIe OFSS file has a special section type ([pf*]) which is used to define physical functions (PFs) in the FIM. Each PF has a dedicated section, where the * character is replaced with the PF number. For example, [pf0], [pf1], etc. For reference FIM configurations, you must have at least 1 PF with 1VF, or 2PFs. This is because the PR region cannot be left unconnected. PFs must be consecutive. The PFVF Limitations table describes the supported number of PFs and VFs.

Table: PF/VF Limitations

| Parameter | Value |

|---|---|

| Min # of PFs | 1 (on PF0) |

| Max # of PFs | 8 |

| Min # of VFs | 0 (if 2PFs are used) |

| Max # of VFs | 2000 distributed across all PFs |

Currently supported configuration options for an OFSS file with IP type pcie are described in the PCIe IP OFSS File Options table.

Table: PCIe IP OFSS File Options

| Section | Parameter | Options | Description |

|---|---|---|---|

[ip] |

type |

pcie |

Specifies that this OFSS file configures the PCIe-SS |

[settings] |

output_name |

pcie_ss |

Specifies the output name of the PCIe-SS IP |

preset |

String | OPTIONAL - Specifies the name of a PCIe-SS IP presets file to use when building the FIM. When used, a presets file will take priority over any other parameters set in this OFSS file. | |

[pf*] |

num_vfs |

Integer | Specifies the number of Virtual Functions in the current PF |

bar0_address_width |

Integer | ||

bar4_address_width |

Integer | ||

vf_bar0_address_width |

Integer | ||

ats_cap_enable |

0 | 1 |

||

vf_ats_cap_enable |

0 | 1 |

||

prs_ext_cap_enable |

0 | 1 |

||

pasid_cap_enable |

0 | 1 |

||

pci_type0_vendor_id |

32'h Value | 0x00008086 |

|

pci_type0_device_id |

32'h Value | 0x0000bcce |

|

revision_id |

32'h Value | 0x00000001 |

|

class_code |

32'h Value | 0x00120000 |

|

subsys_vendor_id |

32'h Value | 0x00008086 |

|

subsys_dev_id |

32'h Value | 0x00001771 |

|

sriov_vf_device_id |

32'h Value | 0x0000bccf |

|

exvf_subsysid |

32'h Value | 0x00001771 |

The default values for all PCIe-SS parameters (that are not defined in the PCIe IP OFSS file) are defined in $OFS_ROOTDIR/ofs-common/tools/ofss_config/ip_params/pcie_ss_component_parameters.py. When using a PCIe IP OFSS file during compilation, the PCIe-SS IP that is used will be defined based on the values in the PCIe IP OFSS file plus the parameters defined in pcie_ss_component_parameters.py.

2.1.2.4 IOPLL IP OFSS File¶

An OFSS file with IP type iopll (e.g. $OFS_ROOTDIR/tools/ofss_config/iopll/iopll.ofss) is used to configure the IOPLL in the FIM.

The IOPLL OFSS file has a special section type ([p_clk]) which is used to define the IOPLL clock frequency.

Currently supported configuration options for an OFSS file with IP type iopll are described in the IOPLL OFSS File Options table.

Table: IOPLL OFSS File Options

| Section | Parameter | Options | Description |

|---|---|---|---|

[ip] |

type |

iopll |

Specifies that this OFSS file configures the IOPLL |

[settings] |

output_name |

sys_pll |

Specifies the output name of the IOPLL. |

instance_name |

iopll_0 |

Specifies the instance name of the IOPLL. | |

[p_clk] |

freq |

Integer: 250 - 470 | Specifies the IOPLL clock frequency in MHz. |

Note: The following frequencies have been tested on reference boards: 350MHz, 400MHz, 470MHz.

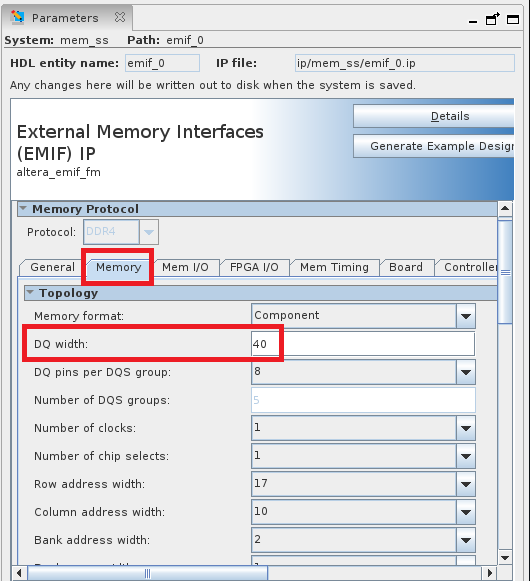

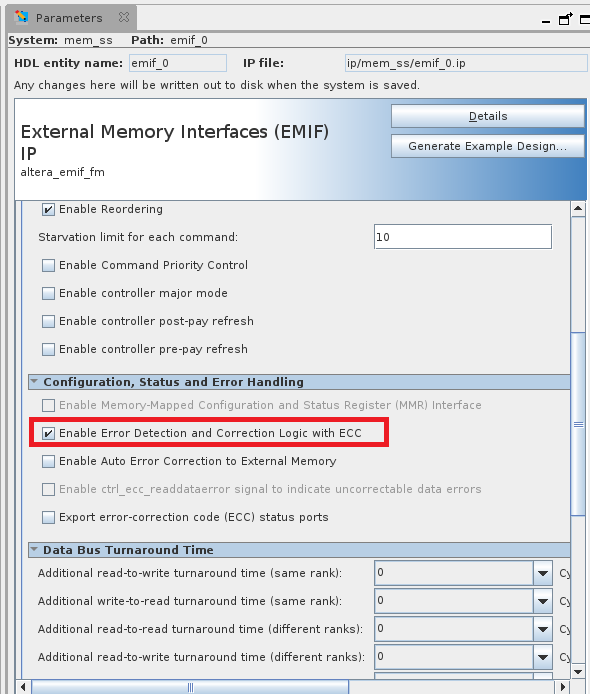

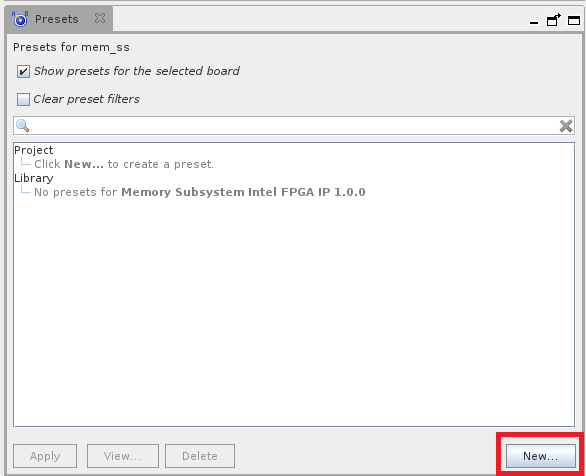

2.1.2.5 Memory IP OFSS File¶

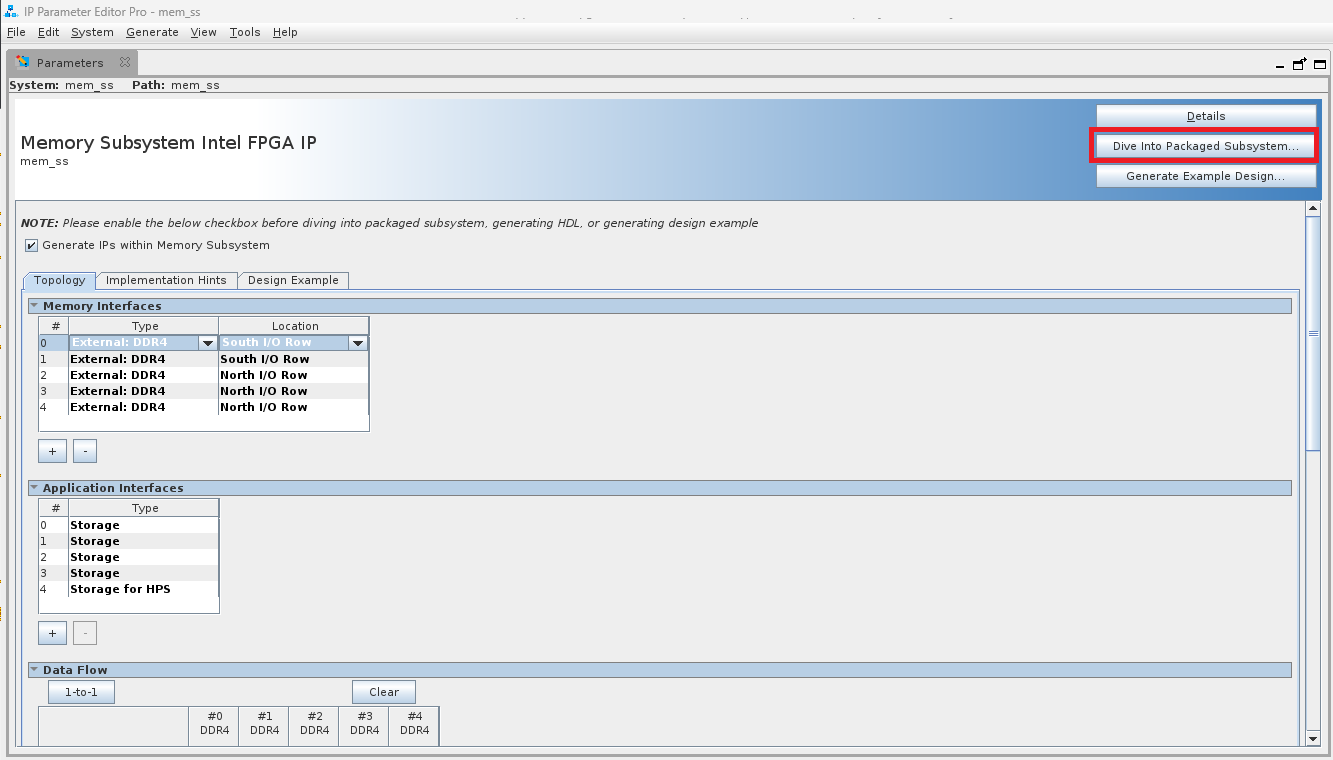

An OFSS file with IP type memory (e.g. $OFS_ROOTDIR/tools/ofss_config/memory/memory.ofss) is used to configure the Memory-SS in the FIM.

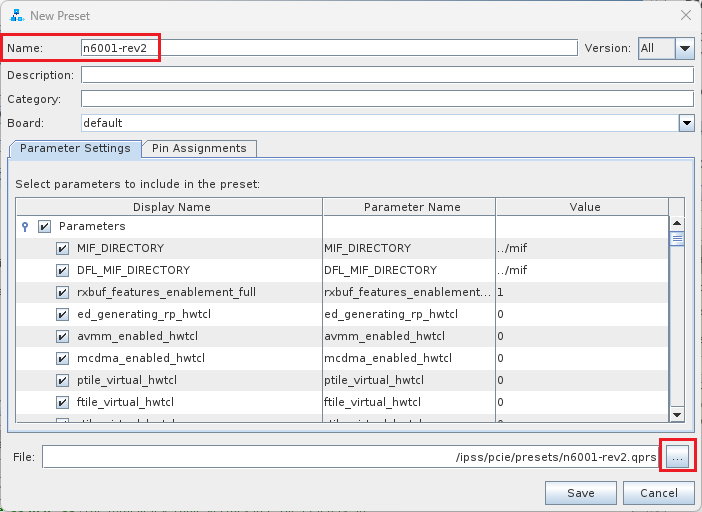

The Memory OFSS file specifies a preset value, which selects a presets file (.qprs) to configure the Memory-SS.

Currently supported configuration options for an OFSS file with IP type memory are described in the Memory OFSS File Options table.

Table: Memory OFSS File Options

| Section | Parameter | Options | Description |

|---|---|---|---|

[ip] |

type |

memory |

Specifies that this OFSS file configures the Memory-SS |

[settings] |

output_name |

mem_ss_fm |

Specifies the output name of the Memory-SS. |

preset |

n6001 | String[1] |

Specifies the name of the .qprs presets file that will be used to build the Memory-SS. |

[1] You may generate your own .qprs presets file with a unique name using Quartus.

Memory-SS presets files are stored in the $OFS_ROOTDIR/ipss/mem/qip/presets directory.

2.1.2.6 HSSI IP OFSS File¶

An OFSS file with IP type hssi (e.g. $OFS_ROOTDIR/tools/ofss_config/hssi/hssi_8x25.ofss) is used to configure the Ethernet-SS in the FIM.

Currently supported configuration options for an OFSS file with IP type hssi are described in the HSSI OFSS File Options table.

Table: HSSI OFSS File Options

| Section | Parameter | Options | Description |

|---|---|---|---|

[ip] |

type |

hssi |

Specifies that this OFSS file configures the Ethernet-SS |

[settings] |

output_name |

hssi_ss |

Specifies the output name of the Ethernet-SS |

num_channels |

Integer | Specifies the number of channels. | |

data_rate |

10GbE | 25GbE | 100GCAUI-4 |

Specifies the data rate | |

preset |

None | String[1] | OPTIONAL - Selects the platform whose preset .qprs file will be used to build the Ethernet-SS. When used, this will overwrite the other settings in this OFSS file. |

[1] You may generate your own .qprs presets file with a unique name using Quartus.

Ethernet-SS presets are stored in $OFS_ROOTDIR/ipss/hssi/qip/hssi_ss/presets directory.

2.1.3 OFS Build Script Outputs¶

The output files resulting from running the the OFS FIM build_top.sh build script are copied to a single directory during the finish stage of the build script. The path for this directory is:

- For N6001:

$OFS_ROOTDIR/<WORK_DIRECTORY>/syn/board/n6001/syn_top/output_files - For N6000:

$OFS_ROOTDIR/<WORK_DIRECTORY>/syn/board/n6000/syn_top/output_files

The output files include programmable images and compilation reports. The OFS Build Script Output Descriptions table describes the images that are generated by the build script.

Table: OFS Build Script Output Descriptions

| File | Description |

|---|---|

| ofs_top[_hps].bin | This is an intermediate, raw binary file. This intermediate raw binary file is produced by taking the Quartus generated .sof file, and converting it to *.pof using quartus_pfg, then converting the *.pof to *.hexout using quartus_cpf, and finally converting the *.hexout to *.bin using objcopy. Depending on whether the FPGA design contains an HPS block, a different file will be generated. **ofs_top.bin* - Raw binary image of the FPGA generated if there is no HPS present in the design. ofs_top_hps.bin - Raw binary image of the FPGA generated if there is an HPS present in the design. |

| ofs_top_page1.bin | This is the binary of the Factory Image and is the input to PACSign utility to generate ofs_top_page1_unsigned.bin binary image file. This image will carry binary content for the HPS if it is included in the SOF image. |

| ofs_top_page0_factory.bin | This is an input file to PACSign to generate ofs_top_page0_unsigned_factory.bin. |

| ofs_top_page0_unsigned_factory.bin | This is the unsigned PACSign output generated for the Factory Image. |

| ofs_top_page1_user1.bin | This is an input file to PACSign to generate ofs_top_page1_unsigned_user1.bin. This file is created by taking the ofs_top_[hps].bin file and assigning the User1 or appending factory block information. |

| ofs_top_page1_unsigned_user1.bin | This is the unsigned FPGA binary image generated by the PACSign utility for the User1 Image. This file is used to load the FPGA flash User1 Image using the fpgasupdate tool. |

| ofs_top_page2_user2.bin | This is an input file to PACSign to generate ofs_top_page2_unsigned_user2.bin. This file is created by taking the ofs_top_[hps].bin file and assigning the User2 or appending factory block information. |

| ofs_top_page2_unsigned_user2.bin | This is the unsigned FPGA binary image generated by the PACSign utility for the User2 Image. This file is used to load the FPGA flash User2 Image using the fpgasupdate tool. |

| ofs_top_hps.sof | If your design contains an Agilex® 7 FPGA Hard Processor System, then the build assembly process combines the FPGA ofs_top.sof programming file with u-boot-spl-dtb.hex to produce this file. |

2.2 Compilation Flows¶

This section provides information for using the build script to generate different FIM types. Walkthroughs are provided for each compilation flow. These walkthroughs require that the development environment has been set up as described in the Set Up Development Environment section.

2.2.1 Flat FIM¶

A flat FIM is compiled such that there is no partial reconfiguration region, and the entire design is built as a flat design. This is useful for compiling new designs without worrying about the complexity introduced by partial reconfiguration. The flat compile removes the PR region and PR IP; thus, you cannot use the -p build flag when using the flat compile setting. Refer to the Compile OFS FIM Section for step-by-step instructions for this flow.

2.2.2 In-Tree PR FIM¶

An In-Tree PR FIM is the default compilation if no compile flags or compile settings are used. This flow will compile the design with the partial reconfiguration region, but it will not create a relocatable PR directory tree to aid in AFU development. Refer to the Compile OFS FIM Section for step-by-step instructions for this flow.

2.2.3 Out-of-Tree PR FIM¶

An Out-of-Tree PR FIM will compile the design with the partial reconfiguration region, and will create a relocatable PR directory tree to aid in AFU workload development. This is especially useful if you are developing a FIM to be used by another team developing AFU workloads. This is the recommended build flow in most cases. There are two ways to create the relocatable PR directory tree:

- Run the FIM build script with the

-poption. Refer to the Compile OFS FIM Section for step-by-step instructions for this flow. - Run the

generate_pr_release.shscript after running the FIM build script. Refer to the Walkthrough: Manually Generate OFS Out-Of-Tree PR FIM Section step-by-step instructions for this flow.

In both cases, the generate_pr_release.sh is run to create the relocatable build tree. This script is located at $OFS_ROOTDIR/ofs-common/scripts/common/syn/generate_pr_release.sh. Usage for this script is as follows:

The Generate PR Release Script Options table describes the options for the generate_pr_release.sh script.

Table: Generate PR Release Script Options

| Parameter | Options | Description |

|---|---|---|

<PATH_OF_RELOCATABLE_PR_TREE> |

String | Specifies the location of the relocatable PR directory tree to be created. |

<BOARD_TARGET> |

n6001 | n6000 | fseries-dk | iseries-dk |

Specifies the name of the board target. |

<WORK_DIRECTORY> |

String | Specifies the existing work directory from which the relocatable PR directory tree will be created from. |

After generating the relocatable build tree, it is located in the $OFS_ROOTDIR/<WORK_DIRECTORY>/pr_build_template directory (or the directory you specified if generated separately). The contents of this directory have the following structure:

├── bin

├── ├── afu_synth

├── ├── qar_gen

├── ├── update_pim

├── ├── run.sh

├── ├── build_env_config

├── README

├── hw

├── ├── lib

├── ├── ├── build

├── ├── ├── fme-ifc-id.txt

├── ├── ├── platform

├── ├── ├── fme-platform-class.txt

├── ├── blue_bits

├── ├── ├── ofs_top_hps.sof

└── ├── ├── ofs_top.sof

2.2.5 Walkthrough: Compile OFS FIM¶

Perform the following steps to compile the OFS Agilex PCIe Attach FIM for n6001 or n6000:

Pre-requisites:

- This walkthrough requires a development environment. Refer to the Set Up Development Environment Section for instructions on setting up a development environment.

Steps:

-

Clone the OFS PCIe Attach FIM repository (or use an existing cloned repository). Refer to the Clone FIM Repository section for step-by-step instructions.

-

Set development environment variables. Refer to the Set Development Environment Variables section for step-by-step instructions.

-

Navigate to the root directory.

-

Run the

build_top.shscript with the desired compile options. Some examples are provided:-

Out-of-Tree PR FIM using OFSS (Standard Flow)

-

N6001

-

N6000

-

-

Flat FIM using OFSS

-

N6001

-

N6000

-

-

In-Tree PR FIM using OFSS

-

N6001

-

N6000

-

-

Flat FIM using OFSS with Host Exercisers Removed

-

N6001

-

N6000

-

-

In-Tree PR FIM using Source

-

N6001

- N6000 - Not supported by default configuration

-

-

-

Once the build script is complete, the build summary should report that the build is complete and passes timing. For example:

2.2.6 Walkthrough: Manually Generate OFS Out-Of-Tree PR FIM¶

This walkthrough describes how to manually generate an Out-Of-Tree PR FIM. This can be automatically done for you if you run the build script with the -p option. This process is not applicable if you run the build script with the flat option.

Pre-requisites:

- This walkthrough requires a development environment. Refer to the Set Up Development Environment Section for instructions on setting up a development environment.

Steps:

-

Clone the OFS PCIe Attach FIM repository (or use an existing cloned repository). Refer to the Clone FIM Repository section for step-by-step instructions.

-

Set development environment variables. Refer to the Set Development Environment Variables section for step-by-step instructions.

-

Navigate to the root directory.

-

Run the

build_top.shscript with the desired compile options using the n6001 OFSS presets. In order to create the relocatable PR tree, you may not compile with theflatoption. For example:-

N6001

-

N6000

-

-

Run the

generate_pr_release.shscript to create the relocatable PR tree.-

N6001

-

N6000

-

2.2.7 Compilation Seed¶

You may change the seed which is used by the build script during Quartus compilation to change the starting point of the fitter. Trying different seeds is useful when your design is failing timing by a small amount.

2.2.7.1 Walkthrough: Change the Compilation Seed¶

Perform the following steps to change the compilation seed for the FIM build.

Pre-requisites:

- This walkthrough requires a development environment. Refer to the Set Up Development Environment Section for instructions on setting up a development environment.

Steps:

-

Clone the OFS PCIe Attach FIM repository (or use an existing cloned repository). Refer to the Clone FIM Repository section for step-by-step instructions.

-

Set development environment variables. Refer to the Set Development Environment Variables section for step-by-step instructions.

-

Edit the

SEEDassignment in the$OFS_ROOTDIR/syn/board/<board_name>/syn_top/ofs_top.qsffile to your desired seed value. The value can be any non-negative integer value.For example, for n6001:

-

Build the FIM. Refer to the Compile OFS FIM section for instructions.

3. FIM Simulation¶

Unit level simulation of key components in the FIM is provided for verification of the following areas:

- Ethernet

- PCIe

- External Memory

- Core FIM

The Unit Level simulations work with Synopsys VCS/VCSMX or Mentor Graphics Questasim simulators. The scripts to run each unit level simulation are located in $OFS_ROOTDIR/sim/unit_test. Each unit test directory contains a README which describes the test in detail.

3.1 Simulation File Generation¶

The simulation files must be generated prior to running unit level simulations. The script to generate simulation files is in the following location:

The usage of the gen_sim_files.sh script is as follows:

The Gen Sim Files Script Options table describes the options for the gen_sim_files.sh script.

Table: Gen Sim Files Script Options

| Field | Options | Description | Requirement |

|---|---|---|---|

--ofss |

<ip_config> |

Used to modify IP, such as the PCIe SS, using .ofss configuration files. More than one .ofss file may be passed to the --ofss switch by concatenating them separated by commas. For example: --ofss config_a.ofss,config_b.ofss. |

Platform Dependent[1] |

<build_target> |

n6001 | n6000 | fseries-dk | iseries-dk |

Specifies which board is being targeted. | Required |

<fim_options> |

null_he_lb | null_he_hssi | null_he_mem | null_he_mem_tg |

Used to change how the FIM is built. - null_he_lb - Replaces the Host Exerciser Loopback (HE_LBK) with he_null. - null_he_hssi - Replaces the Host Exerciser HSSI (HE_HSSI) with he_null. - null_he_mem - Replaces the Host Exerciser Memory (HE_MEM) with he_null. - null_he_mem_tg - Replaces the Host Exerciser Memory Traffic Generator with he_null. More than one FIM option may be passed included in the <fim_options> list by concatenating them separated by commas. For example: <build_target>:null_he_lb,null_he_hssi |

Optional |

<device> |

string | Specifies the device ID for the target FPGA. If not specified, the default device is parsed from the QSF file for the project. |

Optional |

<family> |

string | Specifies the family for the target FPGA. If not specified, the default family is parsed from the QSF file for the project. |

Optional |

[1] Using OFSS is required for the N6000, F-Series Development Kit (2xF-Tile), and the I-Series Development Kit (2xR-Tile, 1xF-Tile).

Refer to the Run Individual Unit Level Simulation section for an example of the simulation files generation flow.

When running regression tests, you may use the -g command line argument to generate simulation files; refer to the Run Regression Unit Level Simulation section for step-by-step instructions.

3.2 Individual Unit Tests¶

Each unit test may be run individually using the run_sim.sh script located in the following directory:

The usage for the run_sim.sh script is as follows:

The Run Sim Script Options table describes the options for the run_sim.sh script.

Table: Run Sim Script Options

| Field | Options | Description |

|---|---|---|

TEST |

String | Specify the name of the test to run, e.g. dfh_walker |

VCSMX |

0 | 1 |

When set, the VCSMX simulator will be used |

MSIM |

0 | 1 |

When set, the QuestaSim simulator will be used |

Note: The default simulator is VCS if neither

VCSMXnorMSIMare set.

The log for a unit test is stored in a transcript file in the simulation directory of the test that was run.

For example, the log for the DFH walker test using VCSMX would be found at:

The simulation waveform database is saved as vcdplus.vpd for post simulation review.

3.2.1 Walkthrough: Run Individual Unit Level Simulation¶

Perform the following steps to run an individual unit test.

Pre-requisites:

- This walkthrough requires a development environment. Refer to the Set Up Development Environment Section for instructions on setting up a development environment.

Steps:

-

Clone the FIM repository (or use an existing cloned repository). Refer to the Clone FIM Repository section for step-by-step instructions.

-

Set development environment variables. Refer to the Set Development Environment Variables section for step-by-step instructions.

-

Navigate to the simulation directory.

-

Generate the simulation files for the target design.

-

N6001

-

N6000

-

-

Navigate to the common simulation directory

-

Run the desired unit test using your desired simulator

-

Using VCS

-

Using VCSMX

-

Using QuestaSim

-

For example, to run the DFH walker test using VCSMX:

-

-

Once the test is complete, check the output for the simulation results. Review the log for detailed test results.

Example output:

Test status: OK ******************** Test summary ******************** test_dfh_walking (id=0) - pass Test passed! Assertion count: 0 $finish called from file "/home/ofs-agx7-pcie-attach/sim/unit_test/scripts/../../bfm/rp_bfm_simple/tester.sv", line 210. $finish at simulation time 356233750000 V C S S i m u l a t i o n R e p o r t Time: 356233750000 fs CPU Time: 57.730 seconds; Data structure size: 47.2Mb Tue Sep 5 09:44:19 2023 run_sim.sh: USER_DEFINED_SIM_OPTIONS +vcs -l ./transcript run_sim.sh: run_sim.sh DONE!

3.3 Regression Unit Tests¶

You may use the regression script regress_run.py to run some or all of the unit tests available with a single command. The regression script is in the following location:

The usage of the regression script is as follows:

regress_run.py [-h] [-l] [-n <num_procs>] [-k <test_package>] [-s <simulator>] [-g] [--ofss <ip_config>] [-b <board_name>] [-e]

The Regression Unit Test Script Options table describes the options for the regress_run.py script.

Table: Regression Unit Test Script Options

| Field | Options | Description |

|---|---|---|

-h | --help |

N/A | Show the help message and exit |

-l | --local |

N/A | Run regression locally |

-n | --n_procs |

Integer | Maximum number of processes/tests to run in parallel when run locally. This has no effect on farm runs. |

-k | --pack |

all | fme | he | hssi | list | mem | pmci |

Test package to run during regression. The "list" option will look for a text file named "list.txt" in the "unit_test" directory for a text list of tests to run (top directory names). The default test package is all. |

-s | --sim |

vcs | vcsmx | msim |

Specifies the simulator used for the regression tests. The default simulator is vcs |

-g | --gen_sim_files |

N/A | Generate simulation files. This only needs to be done once per repo update. This is the equivalent of running the gen_sim_files.sh script. |

-o | --ofss |

<ip_config> |

Used to modify IP, such as the PCIe SS, using .ofss configuration files. More than one .ofss file may be passed to the --ofss switch by concatenating them separated by commas. For example: --ofss config_a.ofss,config_b.ofss. |

-b | --board_name |

n6001 | n6000 | fseries-dk | iseries-dk |

Specifies the board target |

-e | --email_list |

String | Specifies email list to send results to multiple recipients |

The log for each unit test that is run by the regression script is stored in a transcript file in the simulation directory of the test that was run.

For example, the log for the DFH walker test using VCSMX would be found at:

The simulation waveform database is saved as vcdplus.vpd for post simulation review.

3.3.1 Walkthrough: Run Regression Unit Level Simulation¶

Pre-requisites:

- This walkthrough requires a development environment. Refer to the Set Up Development Environment Section for instructions on setting up a development environment.

Steps:

-

Clone the OFS PCIe Attach FIM repository (or use an existing cloned repository). Refer to the Clone FIM Repository section for step-by-step instructions.

-

Set development environment variables. Refer to the Set Development Environment Variables section for step-by-step instructions.

-

Navigate to the unit test scripts directory.

-

Run regression test with the your desired options. For example, to simulate with the options to generate simulation files, run locally, use 8 processes, run all tests, use VCS simulator, and target the desired board:

-

N6001

-

N6000

-

-

Once all tests are complete, check that the tests have passed.

Example output:

2024-02-15 16:06:47,362: Passing Unit Tests:38/38 >>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>> 2024-02-15 16:06:47,362: bfm_test:............................. PASS -- Time Elapsed:0:00:56.125802 2024-02-15 16:06:47,362: csr_test:............................. PASS -- Time Elapsed:0:01:14.072803 2024-02-15 16:06:47,362: dfh_walker:........................... PASS -- Time Elapsed:0:01:00.565714 2024-02-15 16:06:47,362: flr:.................................. PASS -- Time Elapsed:0:00:57.453471 2024-02-15 16:06:47,362: fme_csr_access:....................... PASS -- Time Elapsed:0:00:38.447496 2024-02-15 16:06:47,362: fme_csr_directed:..................... PASS -- Time Elapsed:0:00:47.593359 2024-02-15 16:06:47,362: he_lb_test:........................... PASS -- Time Elapsed:0:01:51.150977 2024-02-15 16:06:47,362: he_mem_lb_test:....................... PASS -- Time Elapsed:0:01:55.940398 2024-02-15 16:06:47,363: he_null_test:......................... PASS -- Time Elapsed:0:09:34.463979 2024-02-15 16:06:47,363: hssi_csr_test:........................ PASS -- Time Elapsed:0:07:18.181326 2024-02-15 16:06:47,363: hssi_kpi_test:........................ PASS -- Time Elapsed:5:45:38.792493 2024-02-15 16:06:47,363: hssi_test:............................ PASS -- Time Elapsed:5:48:39.722731 2024-02-15 16:06:47,363: indirect_csr:......................... PASS -- Time Elapsed:0:00:42.677518 2024-02-15 16:06:47,363: mem_ss_csr_test:...................... PASS -- Time Elapsed:0:00:56.534377 2024-02-15 16:06:47,363: mem_ss_rst_test:...................... PASS -- Time Elapsed:0:00:55.852359 2024-02-15 16:06:47,363: mem_tg_test:.......................... PASS -- Time Elapsed:0:00:55.624567 2024-02-15 16:06:47,363: pcie_ats_basic_test:.................. PASS -- Time Elapsed:0:00:58.659382 2024-02-15 16:06:47,363: pcie_csr_test:........................ PASS -- Time Elapsed:0:00:58.918341 2024-02-15 16:06:47,363: pf_vf_access_test:.................... PASS -- Time Elapsed:0:00:57.045204 2024-02-15 16:06:47,363: pmci_csr_test:........................ PASS -- Time Elapsed:0:01:05.479277 2024-02-15 16:06:47,363: pmci_mailbox_test:.................... PASS -- Time Elapsed:0:02:34.899524 2024-02-15 16:06:47,363: pmci_multi_master_test:............... PASS -- Time Elapsed:0:41:09.670790 2024-02-15 16:06:47,363: pmci_qsfp_telemetry_test:............. PASS -- Time Elapsed:0:40:07.885015 2024-02-15 16:06:47,363: pmci_rd_default_value_test:........... PASS -- Time Elapsed:0:01:06.944379 2024-02-15 16:06:47,363: pmci_ro_mailbox_test:................. PASS -- Time Elapsed:0:10:48.580894 2024-02-15 16:06:47,363: pmci_vdm_b2b_drop_err_scenario_test:.. PASS -- Time Elapsed:0:09:11.081908 2024-02-15 16:06:47,363: pmci_vdm_len_err_scenario_test:....... PASS -- Time Elapsed:0:14:43.763718 2024-02-15 16:06:47,363: pmci_vdm_mctp_mmio_b2b_test:.......... PASS -- Time Elapsed:0:01:45.543515 2024-02-15 16:06:47,363: pmci_vdm_multipkt_error_scenario_test: PASS -- Time Elapsed:1:42:53.665294 2024-02-15 16:06:47,363: pmci_vdm_multipkt_tlp_err_test:....... PASS -- Time Elapsed:0:21:01.225008 2024-02-15 16:06:47,363: pmci_vdm_tlp_error_scenario_test:..... PASS -- Time Elapsed:0:20:36.006368 2024-02-15 16:06:47,363: pmci_vdm_tx_rx_all_random_lpbk_test:.. PASS -- Time Elapsed:0:11:11.355724 2024-02-15 16:06:47,363: pmci_vdm_tx_rx_all_toggle_test:....... PASS -- Time Elapsed:0:08:15.821700 2024-02-15 16:06:47,363: pmci_vdm_tx_rx_lpbk_test:............. PASS -- Time Elapsed:0:08:25.528899 2024-02-15 16:06:47,363: port_gasket_test:..................... PASS -- Time Elapsed:0:00:59.764194 2024-02-15 16:06:47,363: qsfp_test:............................ PASS -- Time Elapsed:0:07:09.847066 2024-02-15 16:06:47,363: remote_stp_test:...................... PASS -- Time Elapsed:0:01:01.852028 2024-02-15 16:06:47,363: uart_csr:............................. PASS -- Time Elapsed:0:01:26.403271 2024-02-15 16:06:47,363: Failing Unit Tests: 0/38 >>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>> 2024-02-15 16:06:47,363: >>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>> 2024-02-15 16:06:47,363: Number of Unit test results captured: 38 2024-02-15 16:06:47,363: Number of Unit test results passing.: 38 2024-02-15 16:06:47,363: Number of Unit test results failing.: 0 2024-02-15 16:06:47,363: End Unit regression running at date/time................: 2024-02-15 16:06:47.363814 2024-02-15 16:06:47,363: Elapsed time for Unit regression run....................: 5:58:50.474807

4. FIM Customization¶

This section describes how to perform specific customizations of the FIM, and provides step-by-step walkthroughs for these customizations. Each walkthrough can be done independently. These walkthroughs require a development environment. Refer to the Set Up Development Environment Section for instructions on setting up a development environment. The FIM Customization Walkthroughs table lists the walkthroughs that are provided in this section. Some walkthroughs include steps for testing on hardware. Testing on hardware requires that you have a deployment environment set up. Refer to the Getting Started Guide: OFS for Agilex® 7 PCIe Attach FPGAs (Intel® FPGA SmartNIC N6001-PL/N6000-PL) for instructions on setting up a deployment environment.

Table: OFS FIM Customization Examples

4.1 Adding a new module to the FIM¶

This section provides a information for adding a custom module to the FIM, simulating the new design, compiling the new design, implementing and testing the new design on hardware, and debugging the new design on hardware.

4.1.1 Hello FIM Theory of Operation¶

If you intend to add a new module to the FIM area, then you will need to inform the host software of the new module. The FIM exposes its functionalities to host software through a set of CSR registers that are mapped to an MMIO region (Memory Mapped IO). This set of CSR registers and their operation is described in FIM MMIO Regions.

See FPGA Device Feature List (DFL) Framework Overview for a description of the software process to read and process the linked list of Device Feature Header (DFH) CSRs within a FPGA.

This example will add a hello_fim module to the design. The Hello FIM example adds a simple DFH register and 64bit scratchpad register connected to the Board Peripheral Fabric (BPF) that can be accessed by the Host. You can use this example as the basis for adding a new feature to your FIM.

For the purposes of this example, the hello_fim module instantiation sets the DFH feature ID (FEAT_ID) to 0x100 which is not currently defined. Using an undefined feature ID will result in no driver being used. Normally, a defined feature ID will be used to associate a specific driver with the FPGA module. Refer to the Device Feature List Feature IDs for a list of DFL feature types and IDs. If you are adding a new module to your design, make sure the Type/ID pair does not conflict with existing Type/ID pairs. You may reserve Type/ID pairs by submitting a pull request at the link above.

The Hello FIM design can be verified by Unit Level simulation, Universal Verification Methodology (UVM) simulation, and running in hardware on the n6001 card. The process for these are described in this section.

4.1.1.1 Hello FIM Board Peripheral Fabric (BPF)¶

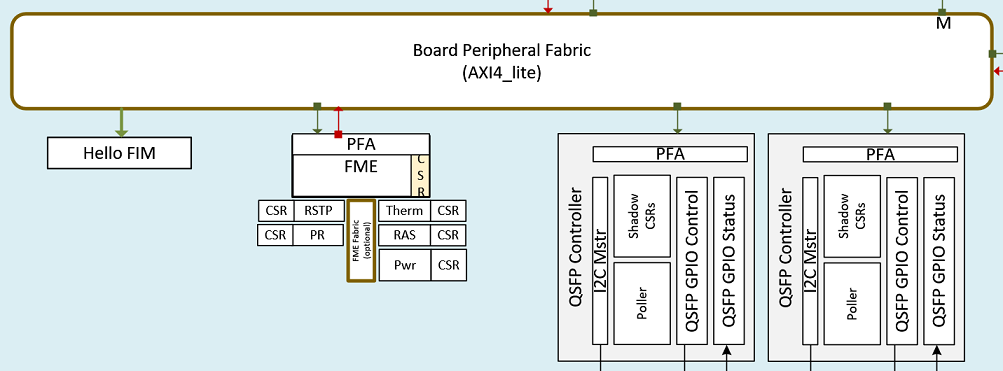

The Hello FIM module will be connected to the Board Peripheral Fabric (BPF), and will be connected such that it can be mastered by the Host. The BPF is an interconnect generated by Platform Designer. The Hello FIM BPF Interface Diagram figure shows the APF/BPF Master/Slave interactions, as well as the added Hello FIM module.

Figure: Hello FIM BPF Interface Diagram

The BPF fabric is defined in $OFS_ROOTDIR/src/pd_qsys/fabric/bpf.txt.

We will add the Hello FIM module to an un-used address space in the MMIO region. The Hello FIM MMIO Address Layout table below shows the MMIO region for the Host with the Hello FIM module added at base address 0x16000.

Table: Hello FIM MMIO Address Layout

| Offset | Feature CSR set |

|---|---|

| 0x00000 | FME AFU |

| 0x10000 | PCIe Interface |

| 0x12000 | QSFP Controller 0 |

| 0x13000 | QSFP Controller 1 |

| 0x14000 | E-Tile Ethernet Interface |

| 0x15000 | EMIF |

| 0x16000 | Hello FIM |

| 0x20000 | PMCI Controller |

| 0x40000 | ST2MM (Streaming to Memory-Mapped) |

| 0x60000 | VUART |

| 0x70000 | PR Control & Status (Port Gasket) |

| 0x71000 | Port CSRs (Port Gasket) |

| 0x72000 | User Clock (Port Gasket) |

| 0x74000 | Remote SignalTap (Port Gasket) |

| 0x80000 | AFU Errors (AFU Interface Handler) |

4.1.1.2 Hello FIM CSR¶

The Hello FIM CSR will consist of the three registers shown in the Hello FIM CSR table below. The DFH and Hello FIM ID registers are read-only. The Scratchpad register supports read and write accesses.

Table: Hello FIM CSR

| Offset | Attribute | Description | Default Value |

|---|---|---|---|

| 0x016000 | RO | DFH(Device Feature Headers) register | 0x30000006a0000100 |

| 0x016030 | RW | Scrachpad register | 0x0 |

| 0x016038 | RO | Hello FIM ID register | 0x6626070150000034 |

4.1.2 Walkthrough: Add a new module to the OFS FIM¶

Perform the following steps to add a new module to the OFS FIM that can be accessed by the Host.

Pre-requisites:

- This walkthrough requires a development environment. Refer to the Set Up Development Environment Section for instructions on setting up a development environment.

Steps:

-

Clone the FIM repository (or use an existing cloned repository). Refer to the Clone FIM Repository section for step-by-step instructions.

-

Set development environment variables. Refer to the Set Development Environment Variables section for step-by-step instructions.

-

Make

hello_fimsource directory -

Create

hello_fim_top.svfile.Copy the following code into

hello_fim_top.sv:// *************************************************************************** // INTEL CONFIDENTIAL // // Copyright (C) 2023 Intel Corporation All Rights Reserved. // // The source code contained or described herein and all documents related to // the source code ("Material") are owned by Intel Corporation or its // suppliers or licensors. Title to the Material remains with Intel // Corporation or its suppliers and licensors. The Material contains trade // secrets and proprietary and confidential information of Intel or its // suppliers and licensors. The Material is protected by worldwide copyright // and trade secret laws and treaty provisions. No part of the Material may be // used, copied, reproduced, modified, published, uploaded, posted, // transmitted, distributed, or disclosed in any way without Intel's prior // express written permission. // // No license under any patent, copyright, trade secret or other intellectual // property right is granted to or conferred upon you by disclosure or // delivery of the Materials, either expressly, by implication, inducement, // estoppel or otherwise. Any license under such intellectual property rights // must be express and approved by Intel in writing. // // You will not, and will not allow any third party to modify, adapt, enhance, // disassemble, decompile, reverse engineer, change or create derivative works // from the Software except and only to the extent as specifically required by // mandatory applicable laws or any applicable third party license terms // accompanying the Software. // // ----------------------------------------------------------------------------- // Engineer : // Create Date : September 2023 // Module Name : hello_fim_top.sv // Project : OFS // ----------------------------------------------------------------------------- // // Description: // This is a simple module that implements DFH registers and // AVMM address decoding logic. module hello_fim_top #( parameter ADDR_WIDTH = 12, parameter DATA_WIDTH = 64, parameter bit [11:0] FEAT_ID = 12'h100, parameter bit [3:0] FEAT_VER = 4'h0, parameter bit [23:0] NEXT_DFH_OFFSET = 24'h1000, parameter bit END_OF_LIST = 1'b0 )( input logic clk, input logic reset, // ----------------------------------------------------------- // AXI4LITE Interface // ----------------------------------------------------------- ofs_fim_axi_lite_if.slave csr_lite_if ); import ofs_fim_cfg_pkg::*; import ofs_csr_pkg::*; //------------------------------------- // Signals //------------------------------------- logic [ADDR_WIDTH-1:0] csr_waddr; logic [DATA_WIDTH-1:0] csr_wdata; logic [DATA_WIDTH/8-1:0] csr_wstrb; logic csr_write; logic csr_slv_wready; csr_access_type_t csr_write_type; logic [ADDR_WIDTH-1:0] csr_raddr; logic csr_read; logic csr_read_32b; logic [DATA_WIDTH-1:0] csr_readdata; logic csr_readdata_valid; logic [ADDR_WIDTH-1:0] csr_addr; logic [63:0] com_csr_writedata; logic com_csr_read; logic com_csr_write; logic [63:0] com_csr_readdata; logic com_csr_readdatavalid; logic [5:0] com_csr_address; // AXI-M CSR interfaces ofs_fim_axi_mmio_if #( .AWID_WIDTH (ofs_fim_cfg_pkg::MMIO_TID_WIDTH), .AWADDR_WIDTH (ADDR_WIDTH), .WDATA_WIDTH (ofs_fim_cfg_pkg::MMIO_DATA_WIDTH), .ARID_WIDTH (ofs_fim_cfg_pkg::MMIO_TID_WIDTH), .ARADDR_WIDTH (ADDR_WIDTH), .RDATA_WIDTH (ofs_fim_cfg_pkg::MMIO_DATA_WIDTH) ) csr_if(); // AXI4-lite to AXI-M adapter axi_lite2mmio axi_lite2mmio ( .clk (clk), .rst_n (~reset), .lite_if (csr_lite_if), .mmio_if (csr_if) ); //--------------------------------- // Map AXI write/read request to CSR write/read, // and send the write/read response back //--------------------------------- ofs_fim_axi_csr_slave #( .ADDR_WIDTH (ADDR_WIDTH), .USE_SLV_READY (1'b1) ) csr_slave ( .csr_if (csr_if), .csr_write (csr_write), .csr_waddr (csr_waddr), .csr_write_type (csr_write_type), .csr_wdata (csr_wdata), .csr_wstrb (csr_wstrb), .csr_slv_wready (csr_slv_wready), .csr_read (csr_read), .csr_raddr (csr_raddr), .csr_read_32b (csr_read_32b), .csr_readdata (csr_readdata), .csr_readdata_valid (csr_readdata_valid) ); // Address mapping assign csr_addr = csr_write ? csr_waddr : csr_raddr; assign com_csr_address = csr_addr[5:0]; // byte address assign csr_slv_wready = 1'b1 ; // Write data mapping assign com_csr_writedata = csr_wdata; // Read-Write mapping always_comb begin com_csr_read = 1'b0; com_csr_write = 1'b0; casez (csr_addr[11:6]) 6'h00 : begin // Common CSR com_csr_read = csr_read; com_csr_write = csr_write; end default: begin com_csr_read = 1'b0; com_csr_write = 1'b0; end endcase end // Read data mapping always_comb begin if (com_csr_readdatavalid) begin csr_readdata = com_csr_readdata; csr_readdata_valid = 1'b1; end else begin csr_readdata = '0; csr_readdata_valid = 1'b0; end end hello_fim_com #( .FEAT_ID (FEAT_ID), .FEAT_VER (FEAT_VER), .NEXT_DFH_OFFSET (NEXT_DFH_OFFSET), .END_OF_LIST (END_OF_LIST) ) hello_fim_com_inst ( .clk (clk ), .reset (reset ), .writedata (com_csr_writedata ), .read (com_csr_read ), .write (com_csr_write ), .byteenable (4'hF ), .readdata (com_csr_readdata ), .readdatavalid (com_csr_readdatavalid ), .address (com_csr_address ) ); endmodule -

Create

hello_fim_com.svfile.Copy the following code to

hello_fim_com.sv:module hello_fim_com #( parameter bit [11:0] FEAT_ID = 12'h100, parameter bit [3:0] FEAT_VER = 4'h0, parameter bit [23:0] NEXT_DFH_OFFSET = 24'h1000, parameter bit END_OF_LIST = 1'b0 )( input clk, input reset, input [63:0] writedata, input read, input write, input [3:0] byteenable, output reg [63:0] readdata, output reg readdatavalid, input [5:0] address ); wire reset_n = !reset; reg [63:0] rdata_comb; reg [63:0] scratch_reg; always @(negedge reset_n ,posedge clk) if (!reset_n) readdata[63:0] <= 64'h0; else readdata[63:0] <= rdata_comb[63:0]; always @(negedge reset_n , posedge clk) if (!reset_n) readdatavalid <= 1'b0; else readdatavalid <= read; wire wr = write; wire re = read; wire [5:0] addr = address[5:0]; wire [63:0] din = writedata [63:0]; wire wr_scratch_reg = wr & (addr[5:0] == 6'h30)? byteenable[0]:1'b0; // 64 bit scratch register always @( negedge reset_n, posedge clk) if (!reset_n) begin scratch_reg <= 64'h0; end else begin if (wr_scratch_reg) begin scratch_reg <= din; end end always @ (*) begin rdata_comb = 64'h0000000000000000; if(re) begin case (addr) 6'h00 : begin rdata_comb [11:0] = FEAT_ID ; // dfh_feature_id is reserved or a constant value, a read access gives the reset value rdata_comb [15:12] = FEAT_VER ; // dfh_feature_rev is reserved or a constant value, a read access gives the reset value rdata_comb [39:16] = NEXT_DFH_OFFSET ; // dfh_dfh_ofst is reserved or a constant value, a read access gives the reset value rdata_comb [40] = END_OF_LIST ; //dfh_end_of_list rdata_comb [59:40] = 20'h00000 ; // dfh_rsvd1 is reserved or a constant value, a read access gives the reset value rdata_comb [63:60] = 4'h3 ; // dfh_feat_type is reserved or a constant value, a read access gives the reset value end 6'h30 : begin rdata_comb [63:0] = scratch_reg; end 6'h38 : begin rdata_comb [63:0] = 64'h6626_0701_5000_0034; end default : begin rdata_comb = 64'h0000000000000000; end endcase end end endmodule -

Create

hello_fim_design_files.tclfile.Copy the following code into

hello_fim_design_files.tcl# Copyright 2023 Intel Corporation. # # THIS SOFTWARE MAY CONTAIN PREPRODUCTION CODE AND IS PROVIDED BY THE # COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" AND ANY EXPRESS OR IMPLIED # WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF # MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE # DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT HOLDER OR CONTRIBUTORS BE # LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR # CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF # SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR # BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, # WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE # OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, # EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE. # # Hello FIM Files #-------------------- set_global_assignment -name SYSTEMVERILOG_FILE $::env(BUILD_ROOT_REL)/src/hello_fim/hello_fim_com.sv set_global_assignment -name SYSTEMVERILOG_FILE $::env(BUILD_ROOT_REL)/src/hello_fim/hello_fim_top.sv -

Modify

ofs_top.qsffor the target board to include Hello FIM module-

N6001

-

N6000

Add the following line:

-

-

Modify

ofs_top_sources.tclfor the target board to include Hello FIM design files-

N6001

-

N6000

Add the following line:

-

-

Modify

fabric_design_files.tclto include BPF Hello FIM Slave IP.Add the following line:

-

Modify

fabric_width_pkg.svto add Hello FIM slave information and update EMIF slave next offset.-

Open

fabric_width_pkg.sv -

Add/modify the following lines:

-

-

Modify

top.svto support the Hello FIM module.-

Open

top.sv -

Add

bpf_hello_fim_slv_ifto AXI interfaces -

Add Hello FIM instantiation

//******************************* // Hello FIM Subsystem //******************************* `ifdef INCLUDE_HELLO_FIM hello_fim_top #( .ADDR_WIDTH (fabric_width_pkg::bpf_hello_fim_slv_address_width), .DATA_WIDTH (64), .FEAT_ID (12'h100), .FEAT_VER (4'h0), .NEXT_DFH_OFFSET (fabric_width_pkg::bpf_hello_fim_slv_next_dfh_offset), .END_OF_LIST (fabric_width_pkg::bpf_hello_fim_slv_eol) ) hello_fim_top_inst ( .clk (clk_csr), .reset(~rst_n_csr), .csr_lite_if (bpf_hello_fim_slv_if) ); `else dummy_csr #( .FEAT_ID (12'h100), .FEAT_VER (4'h0), .NEXT_DFH_OFFSET (fabric_width_pkg::bpf_hello_fim_slv_next_dfh_offset), .END_OF_LIST (fabric_width_pkg::bpf_hello_fim_slv_eol) ) hello_fim_dummy ( .clk (clk_csr), .rst_n (rst_n_csr), .csr_lite_if (bpf_hello_fim_slv_if) ); `endif -

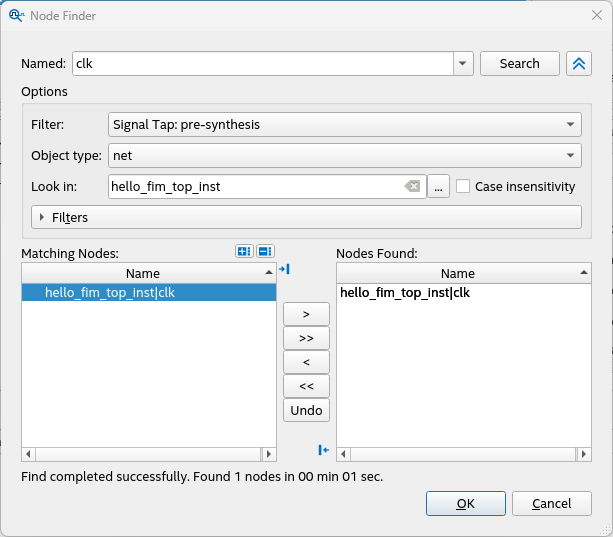

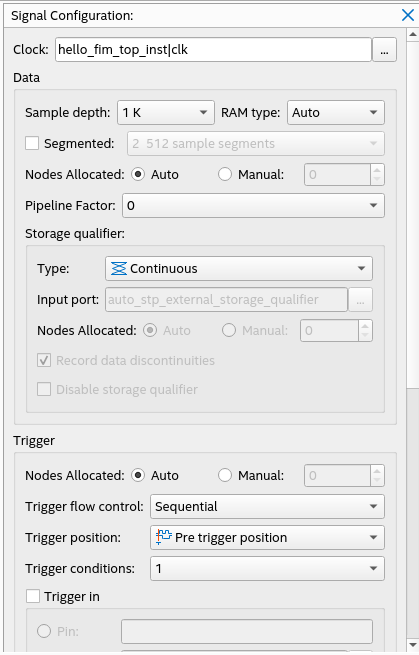

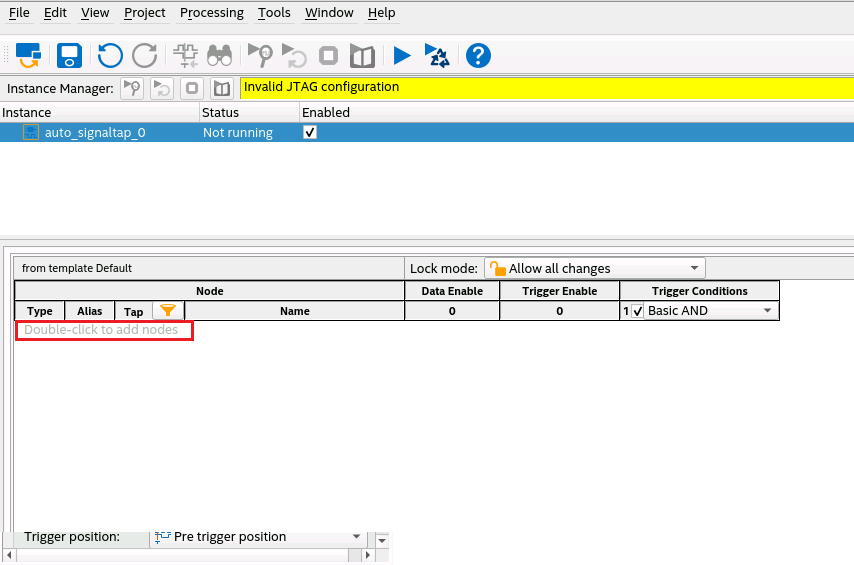

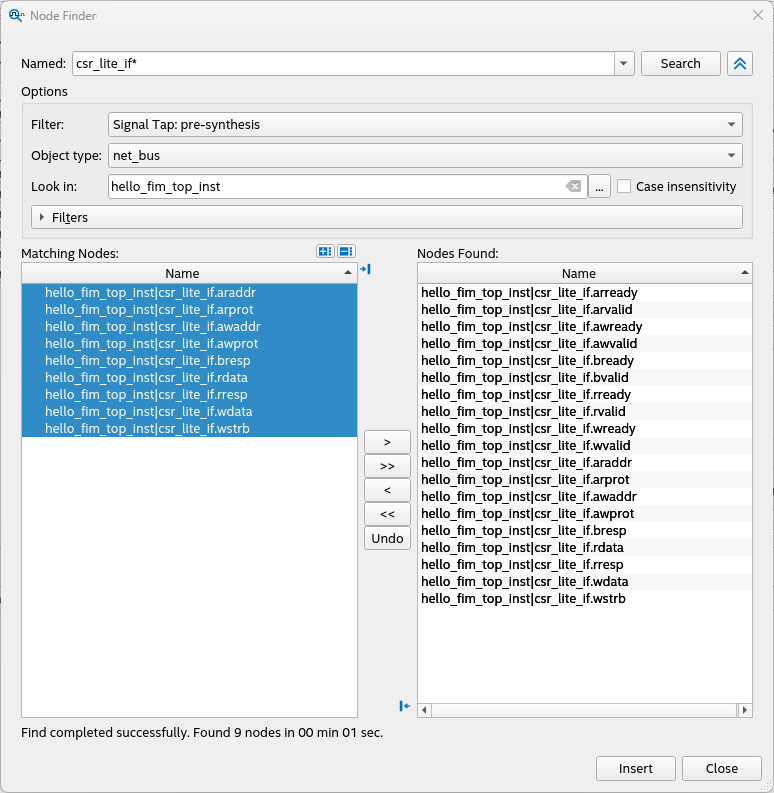

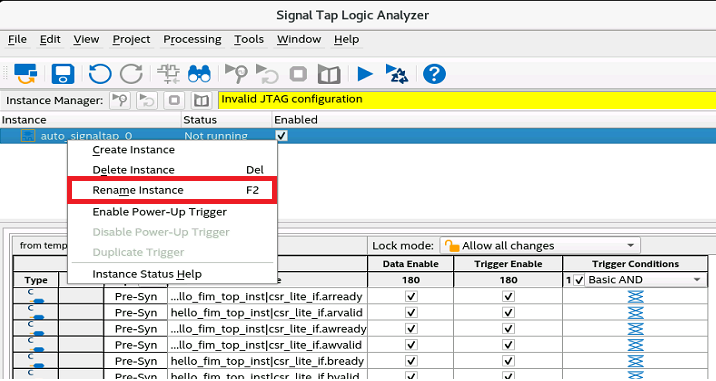

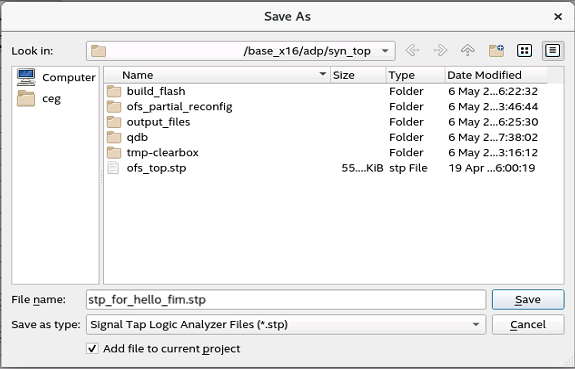

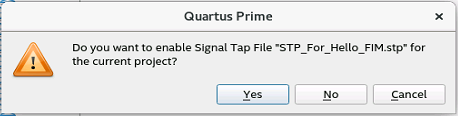

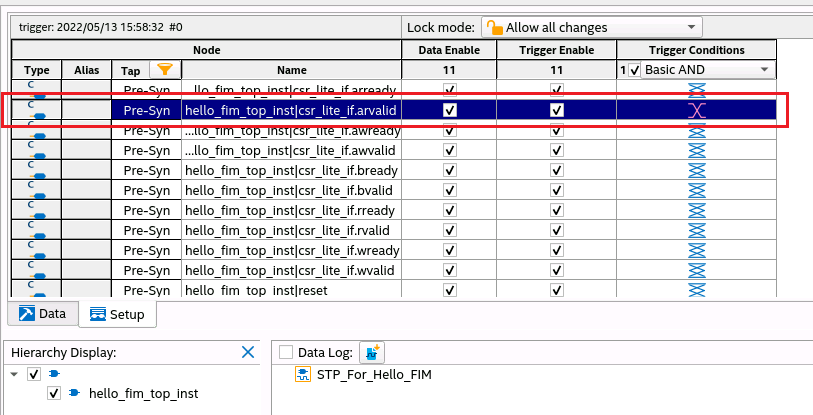

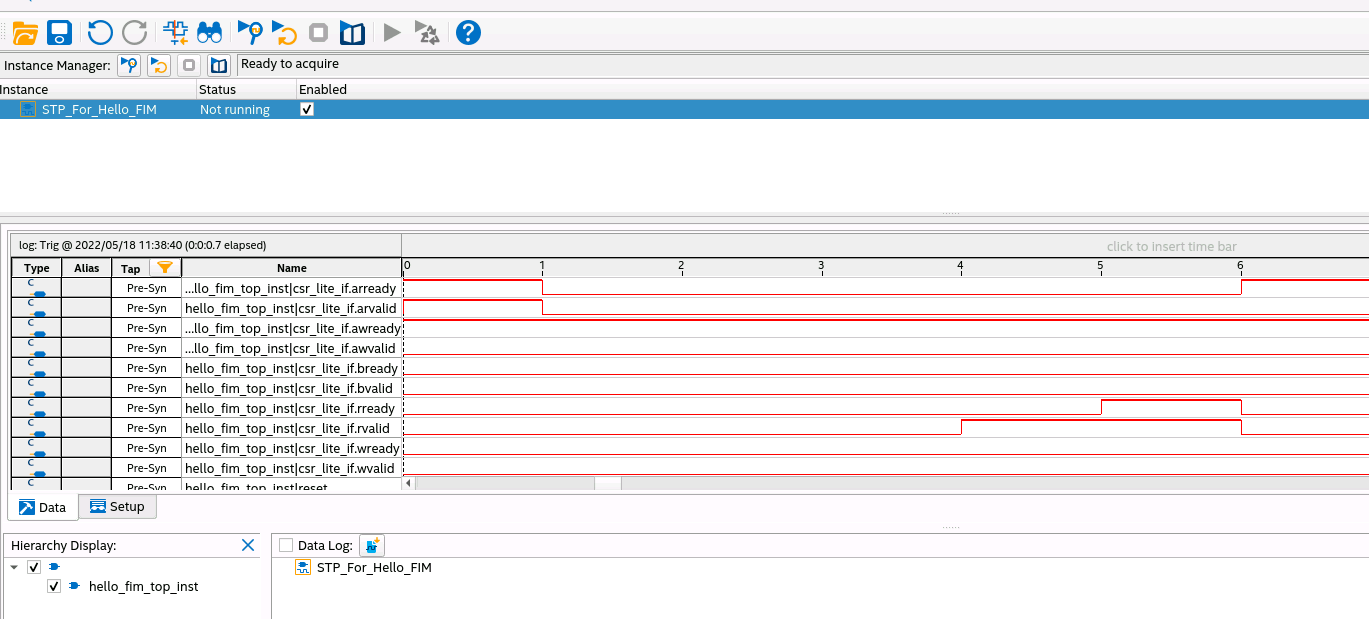

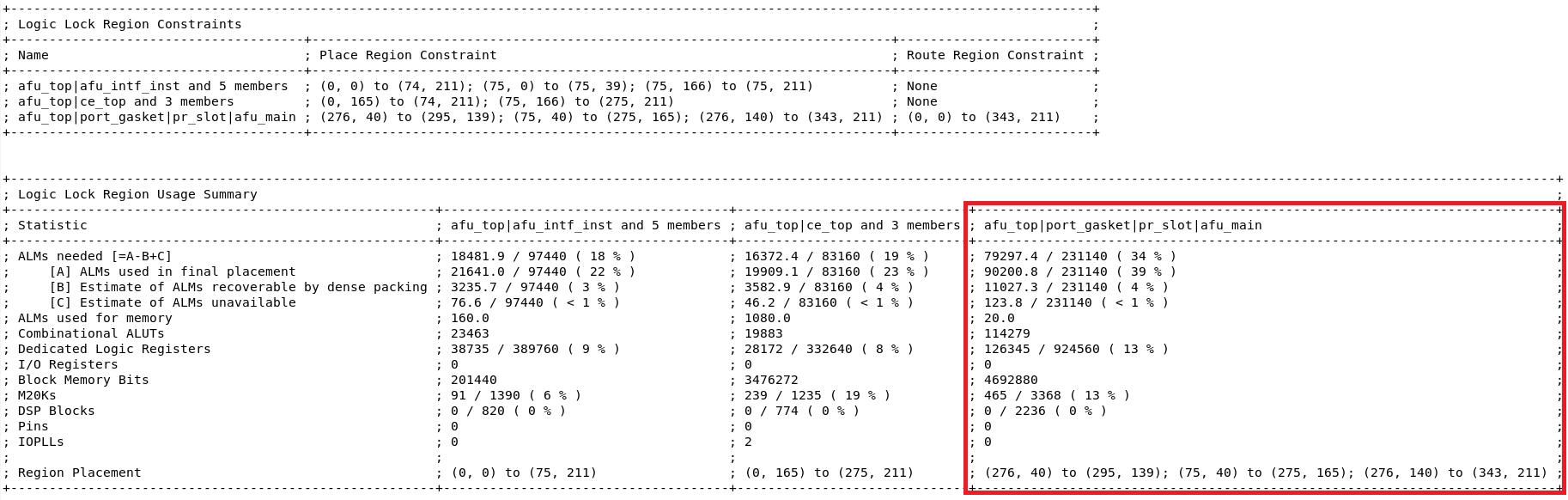

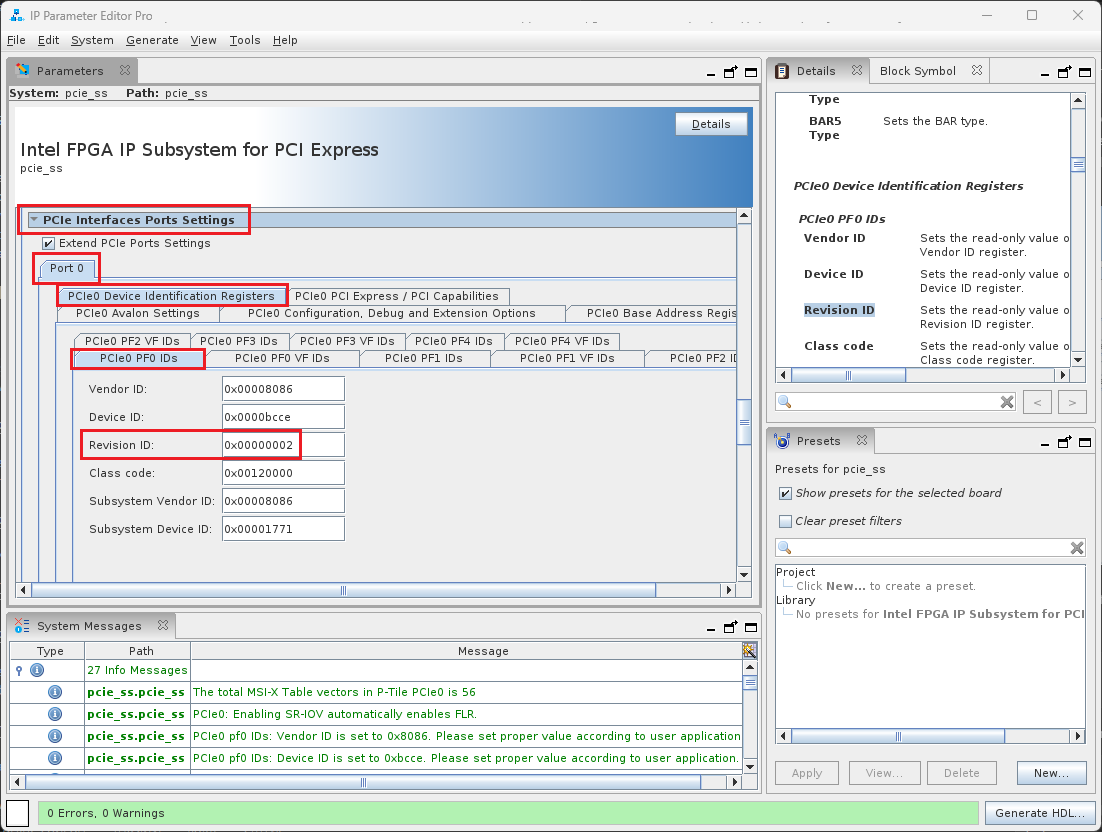

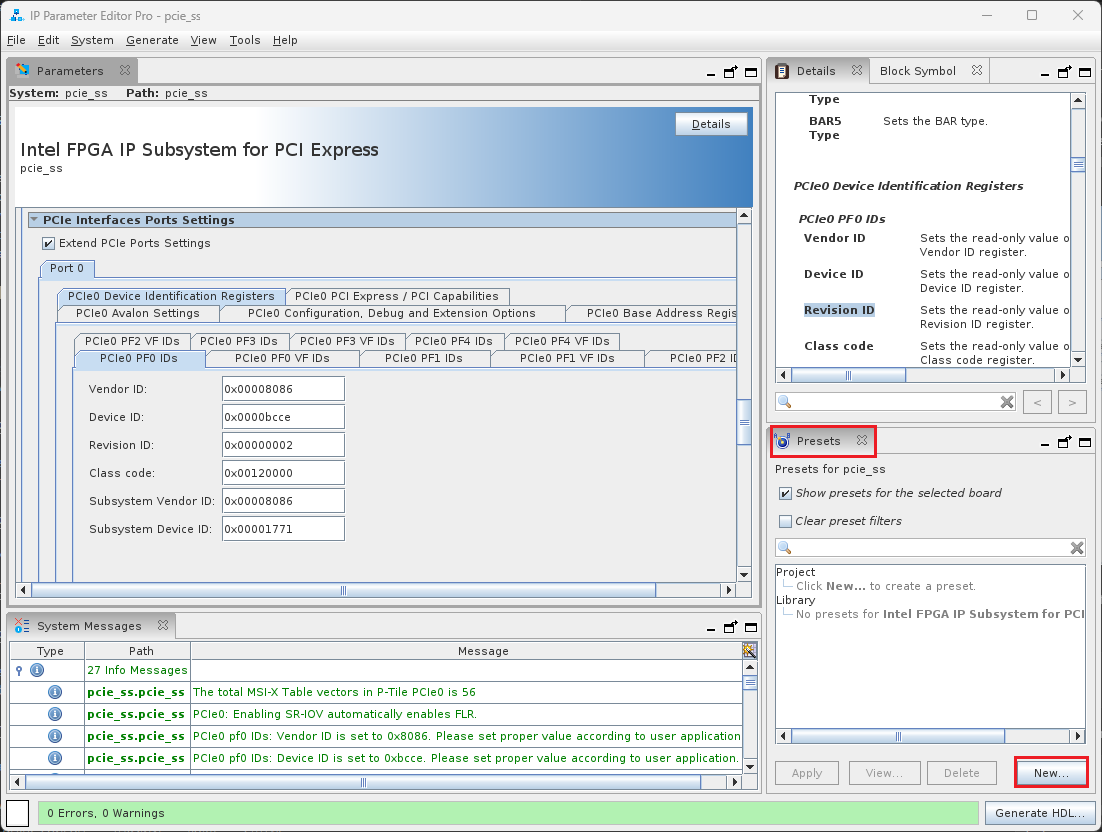

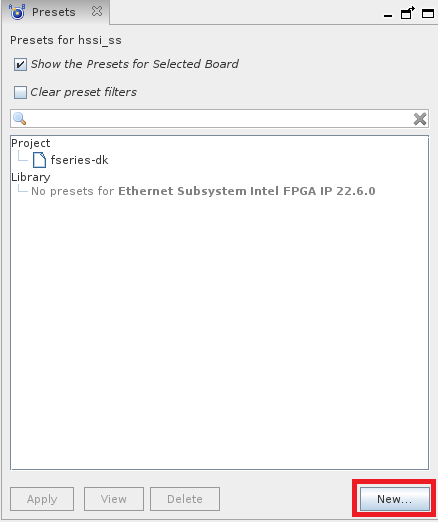

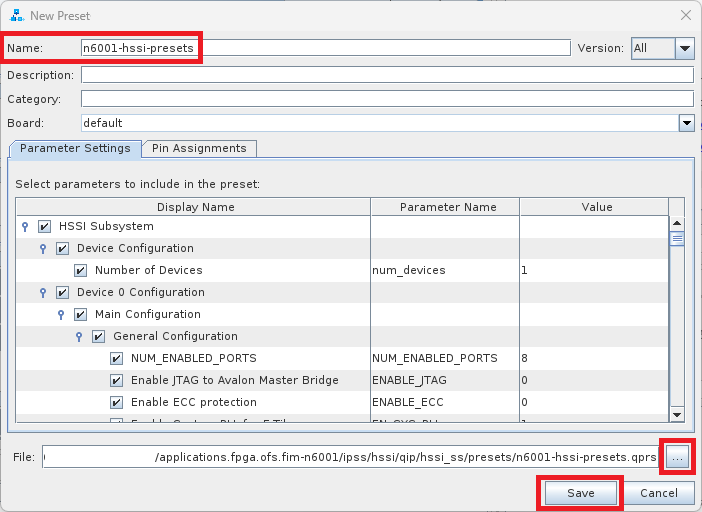

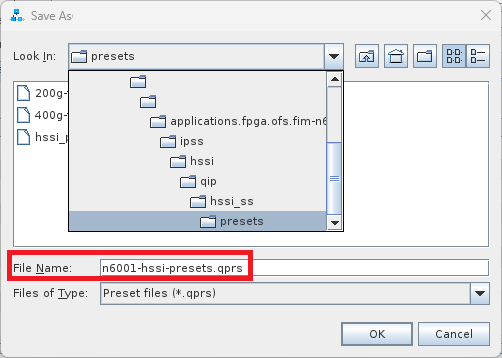

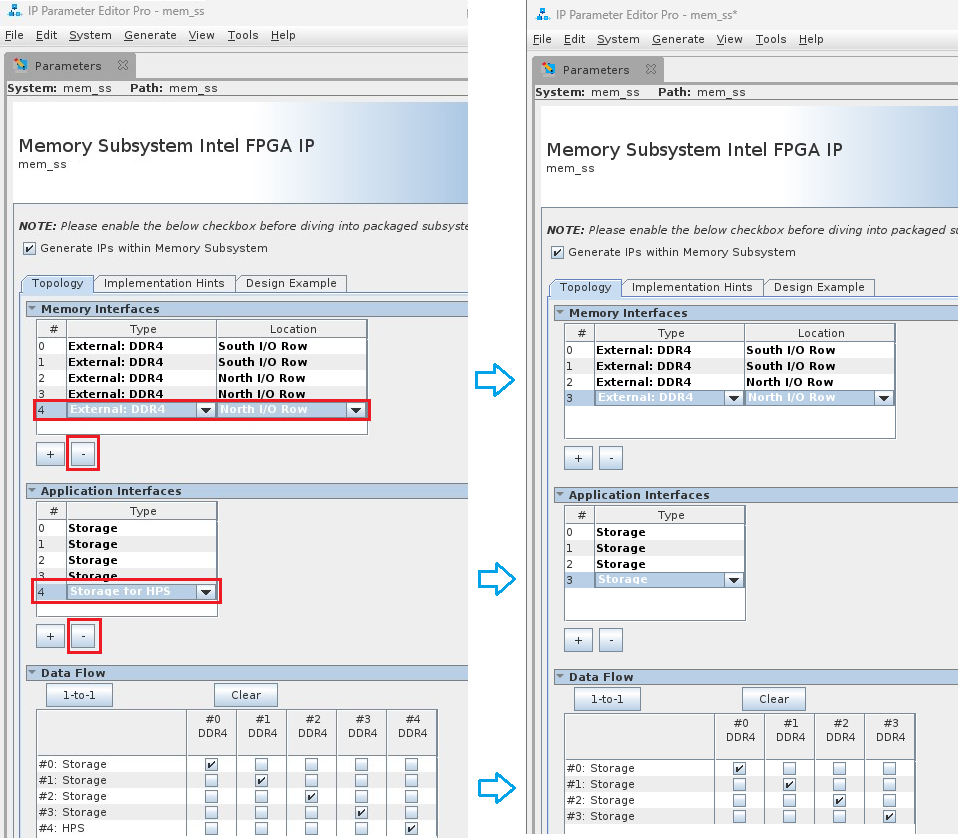

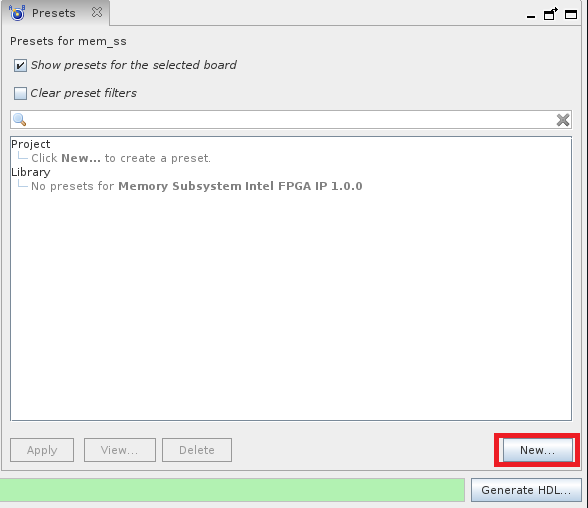

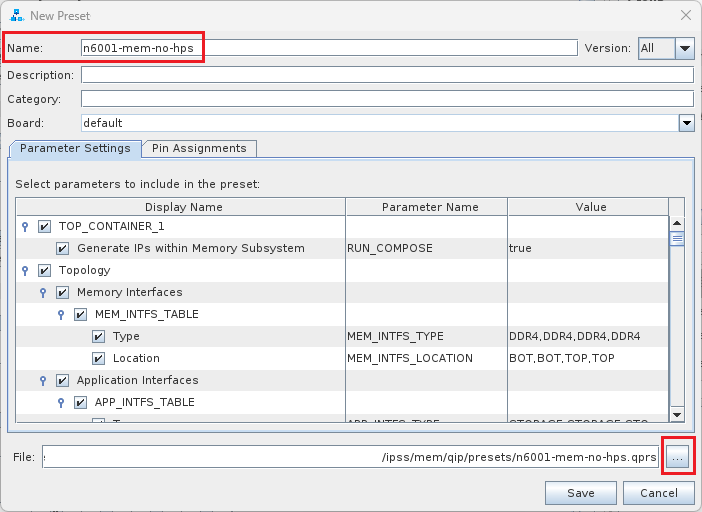

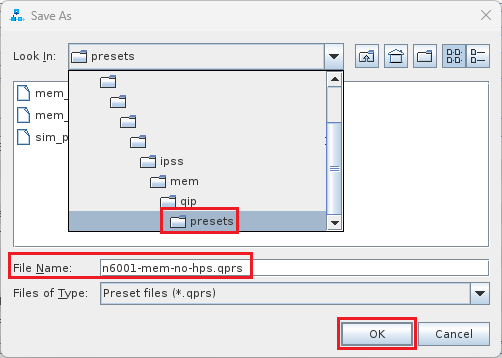

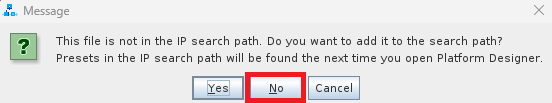

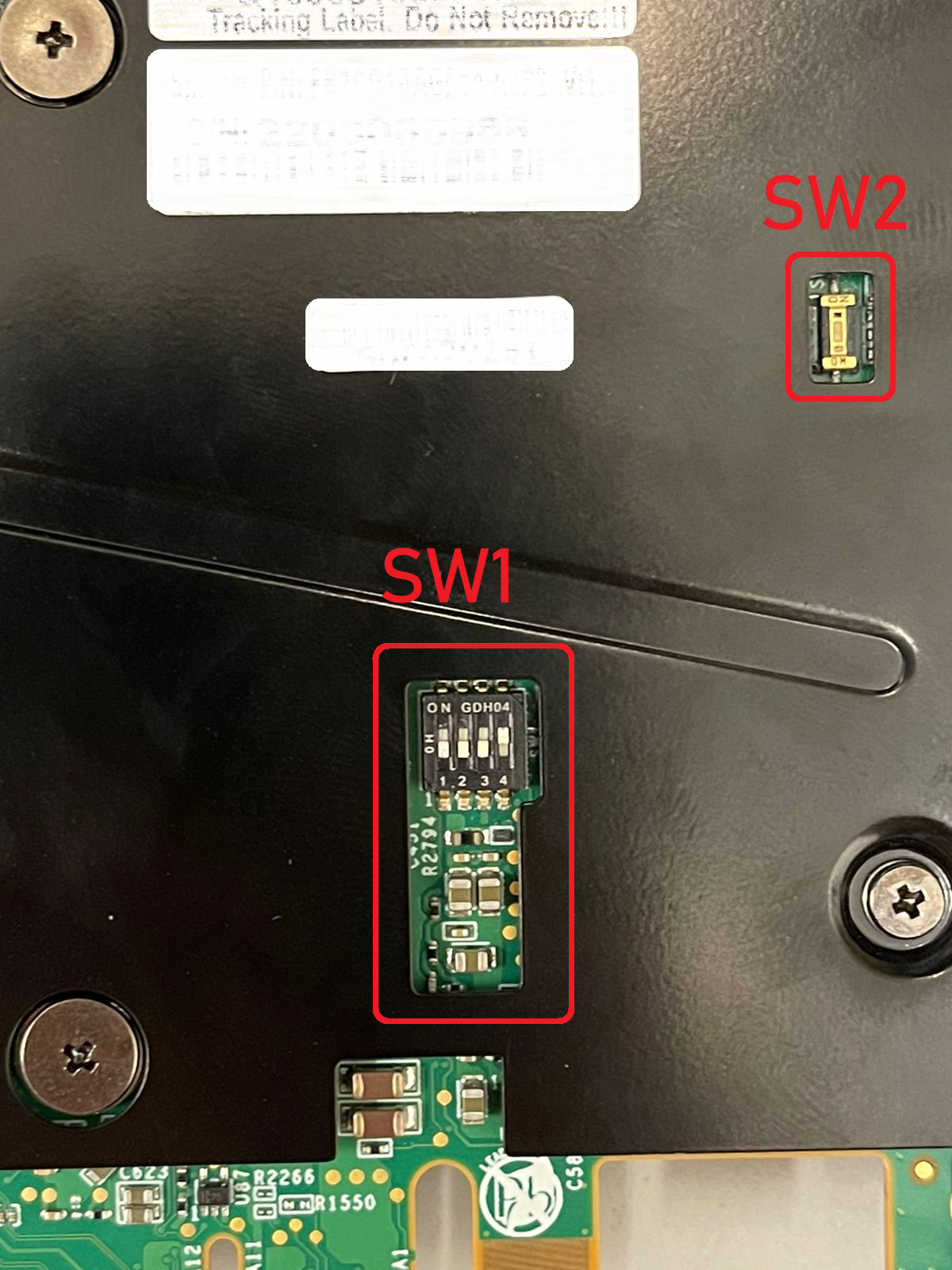

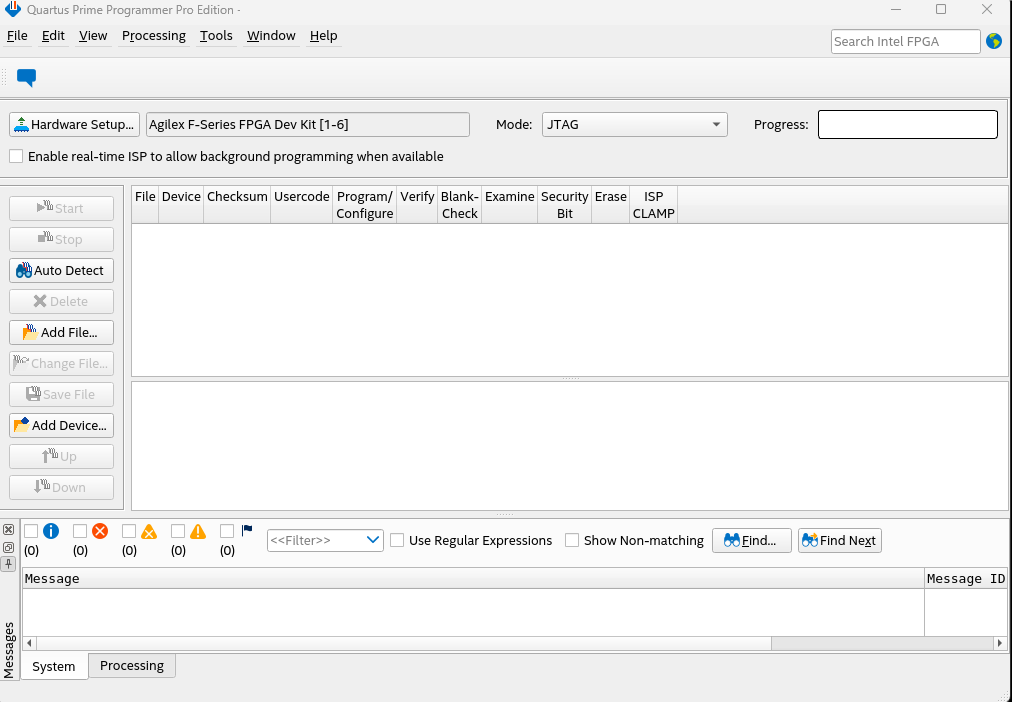

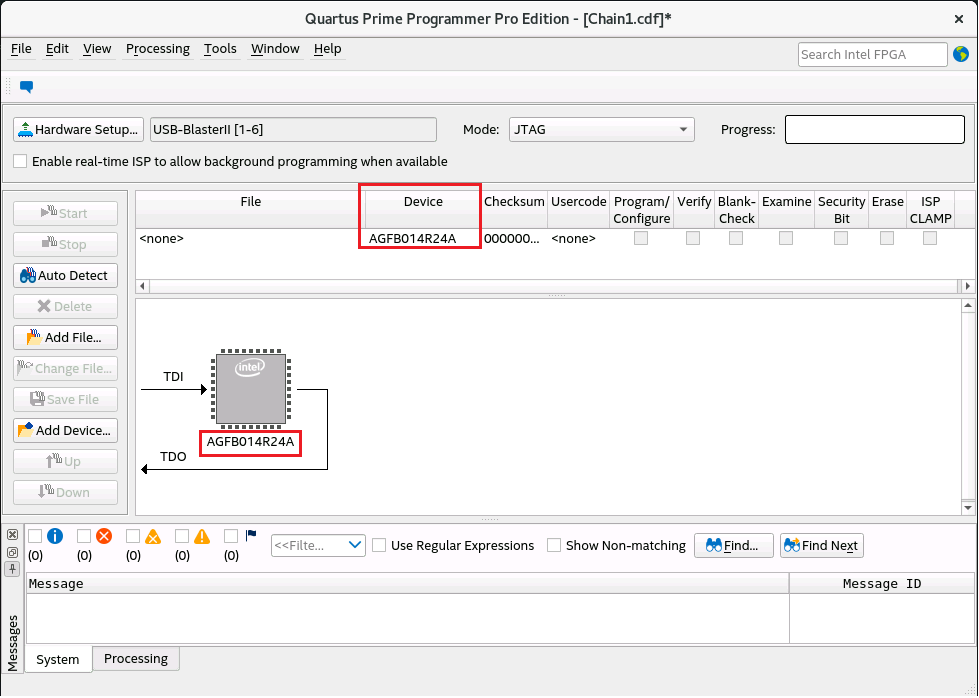

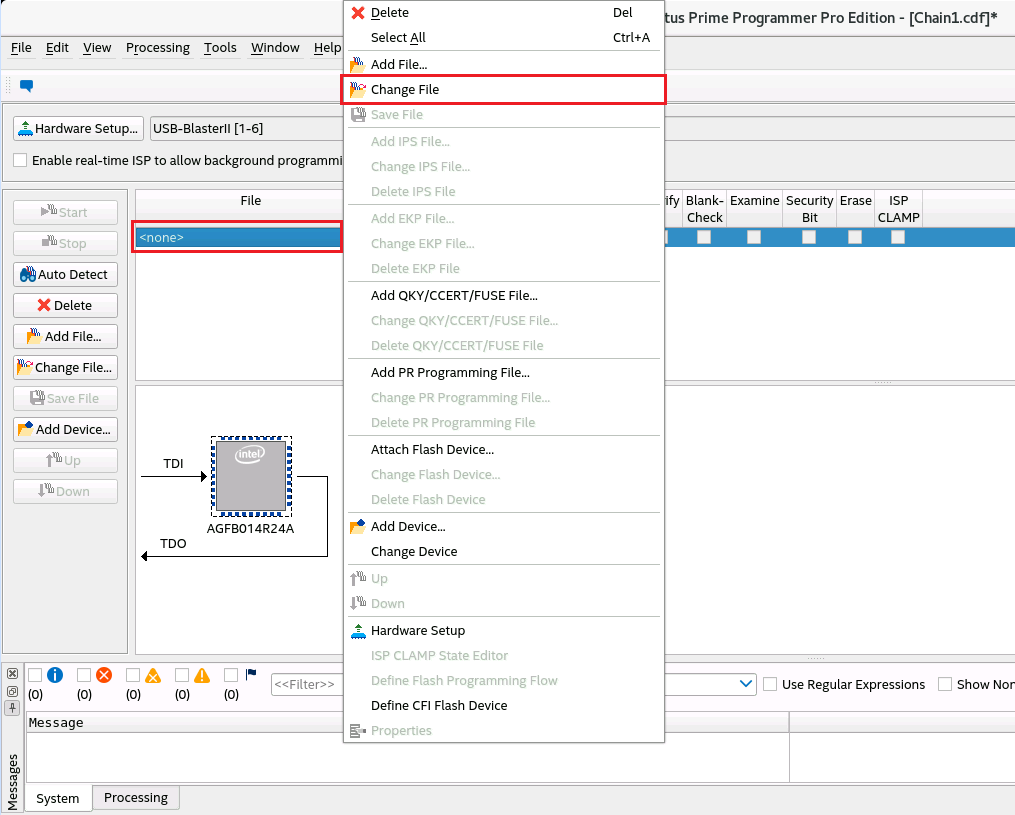

Add interfaces for Hello FIM slv to bpf instantiation